CS61C学习笔记(七)-同步数字系统之状态

关于状态

状态电路与组合逻辑电路:

- 状态电路用于记住值,如寄存器(小而快)或内存(大而慢)。

- 组合逻辑电路用于处理数据流。

状态的使用

- 作为存储某些不确定时间价值的场所:

- 寄存器文件(如RISC - V上的x0 - x31)

- 记忆(缓存和主存)

- 帮助控制组合逻辑块之间的信息流动。

- 状态变量用于在组合逻辑块的输入端保持信息的运动,并允许有序的传递。

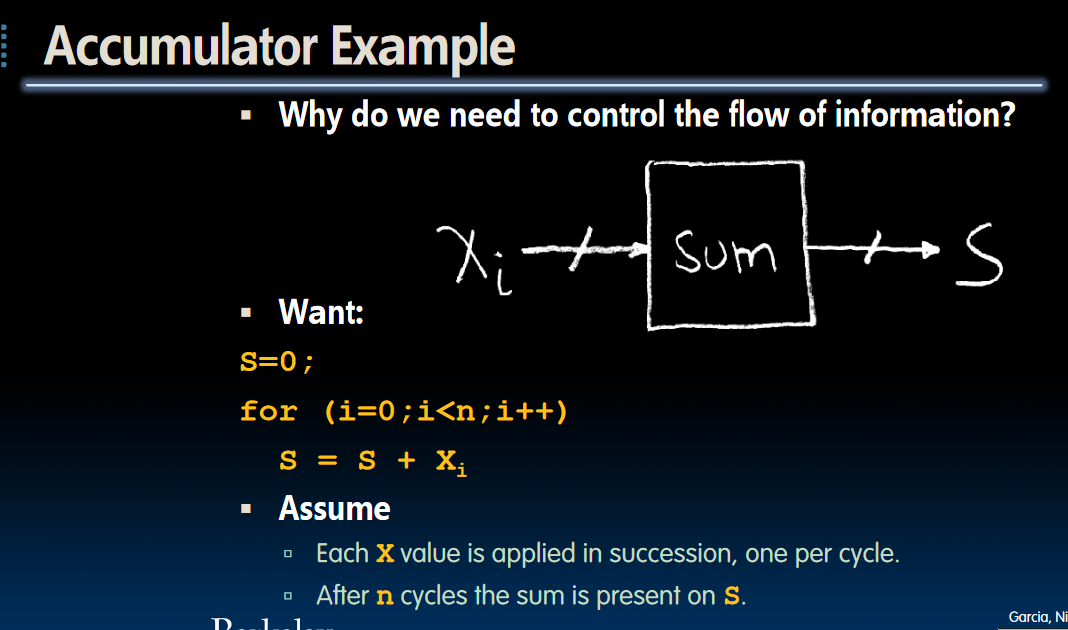

构建累加器

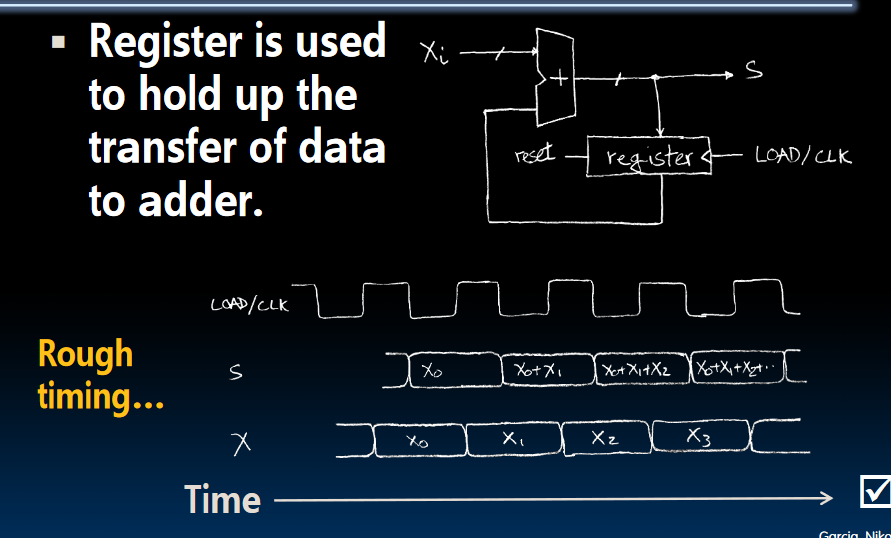

在register这块中,数据从上到下,从右到左

刚开始时,reset初始化sum为0,随后sum和xi进行加法运算,sum再次进入register后传给xi

累加器的构建:

- 累加器的目标是将一系列输入值累加。

- 基本思路是通过循环累加输入数组中的每个元素,最终得到总和。

累加器的初步设计:

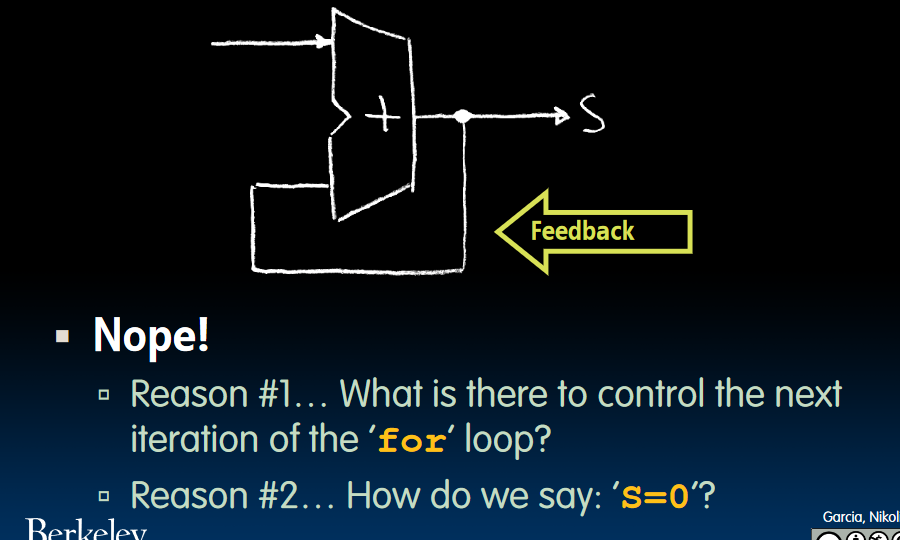

- 设计一个简单的累加电路,尝试在没有状态电路的情况下进行累加。

- 发现仅使用组合逻辑电路无法完成累加操作,因为无法控制循环的迭代,也无法初始化累加器。

引入状态电路:

- 为了解决上述问题,引入寄存器和复位线。

- 寄存器用于保存当前累加值,并在复位时将其设为零。

- 加载器(时钟)控制每个周期的累加操作。

反馈机制的使用:

- 反馈机制允许输出值回送到输入,用于连续累加。

- 通过在时钟的上升沿进行操作,确保累加过程有序进行。

具体实现:

- 累加器电路图示,显示输入值(x)随着时间变化。

- 通过时钟控制寄存器,使累加值逐步增加。

总结与预告:

- 讲座结束时展示了累加器的工作原理。

- 预告下一讲将进一步深入探讨累加器的具体实现。

关键概念

- 状态电路(State Circuit):用于记忆和存储数据的电路。

- 组合逻辑电路(Combinational Logic Circuit):用于处理和传递数据的电路。

- 累加器(Accumulator):一个用于累加输入值的电路。

- 反馈(Feedback):输出值返回到输入的机制,用于连续处理。

- 寄存器(Register):用于存储数据的基本单元。

- 时钟(Clock):控制电路操作时序的信号。

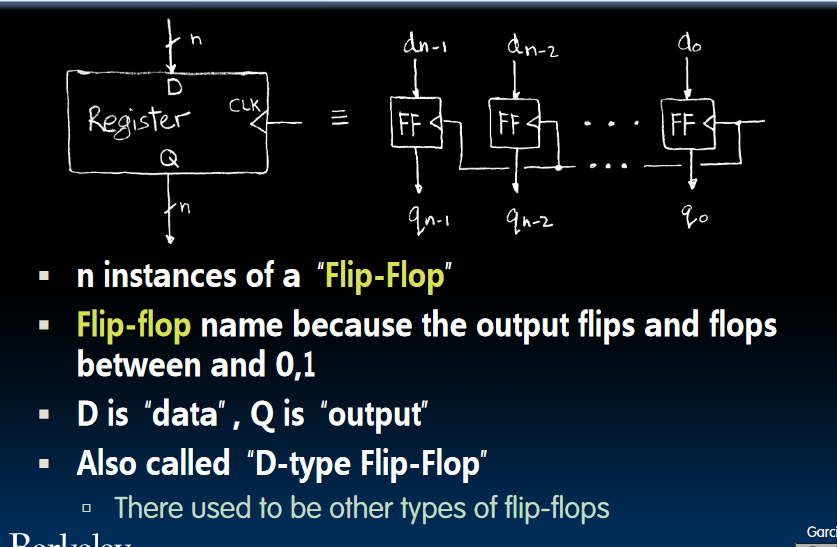

寄存器细节-触发器(Flip-flops)

flip and flop between 0 and 1.

触发器的基本概念

- 寄存器的内部是触发器(Flip-Flops):

- 一个n位寄存器实际上是n个1位触发器的并行组合。

- 输入称为数据(Data, D),输出称为Q(代表静止Quiescent)。

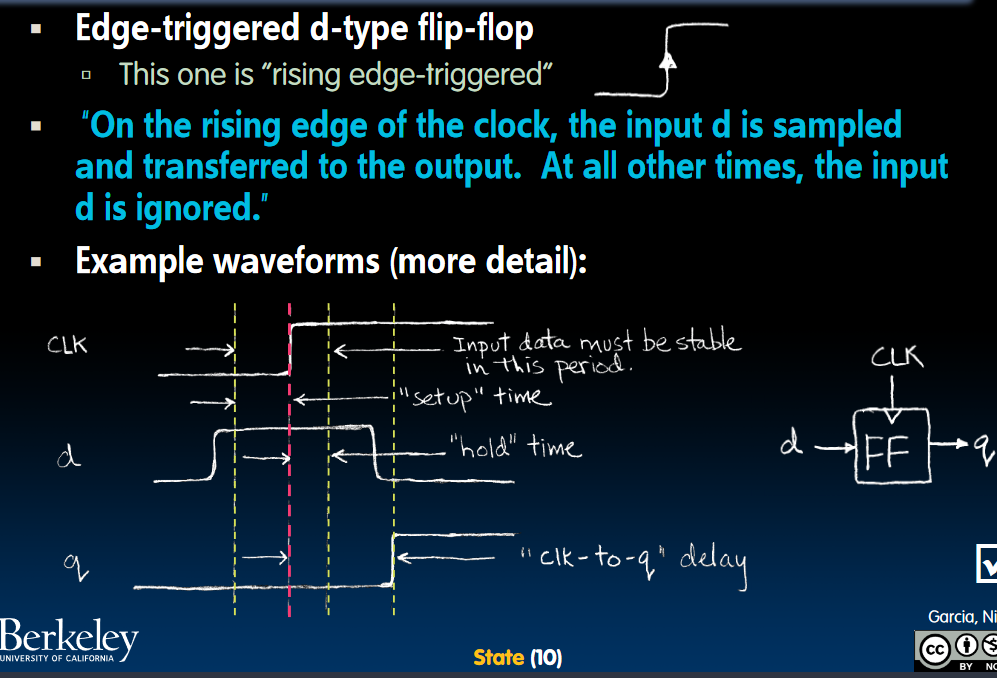

触发器(FF)的时序

这个是上升沿触发触发器(rising edge-triggered),还有下降沿触发触发器,在这里我们只考虑上升沿触发的触发器、也称为正边沿(positive edge)。

这意味着当它 从 0 变为 1 时,就会触发,即负载的意思。

触发器的工作原理

触发器的输入输出:

- 输入数据通过触发器的时钟信号在上升沿被采样。

- 输出数据在触发器采样后的某个延迟时间内传输到输出端。

- 上升沿触发(Rising Edge Triggered):在时钟信号从0到1的上升沿时采样输入数据。

时序图解释:

- 时钟信号的上升沿是触发器工作的关键时刻。

- 在上升沿时,触发器采样输入数据并将其传输到输出端。

- 输入数据可以在两个时钟信号之间变化,但触发器只在上升沿时采样。

触发器的时间参数

- 设置时间(Setup Time):

- 输入数据在时钟上升沿之前必须保持稳定的时间。

- 保持时间(Hold Time):

- 输入数据在时钟上升沿之后必须保持稳定的时间。

- 时钟到输出延迟(Clock to Q Delay):

- 从时钟上升沿到输出数据稳定所需的时间。

理想情况下触发器的参数要求

- 较小的时钟到输出延迟:

- 延迟越小,电路运行速度越快。

- 较小的设置和保持时间:

- 稳定输入数据的时间窗口越小越好。

- 输入数据能被快速采样并传输到输出端。

总结

- 触发器是寄存器的基本组成单元,通过时钟信号的上升沿采样输入数据,并在一定延迟后输出。

- 理想的触发器需要较小的设置时间、保持时间和时钟到输出延迟,以实现更快、更稳定的电路性能。

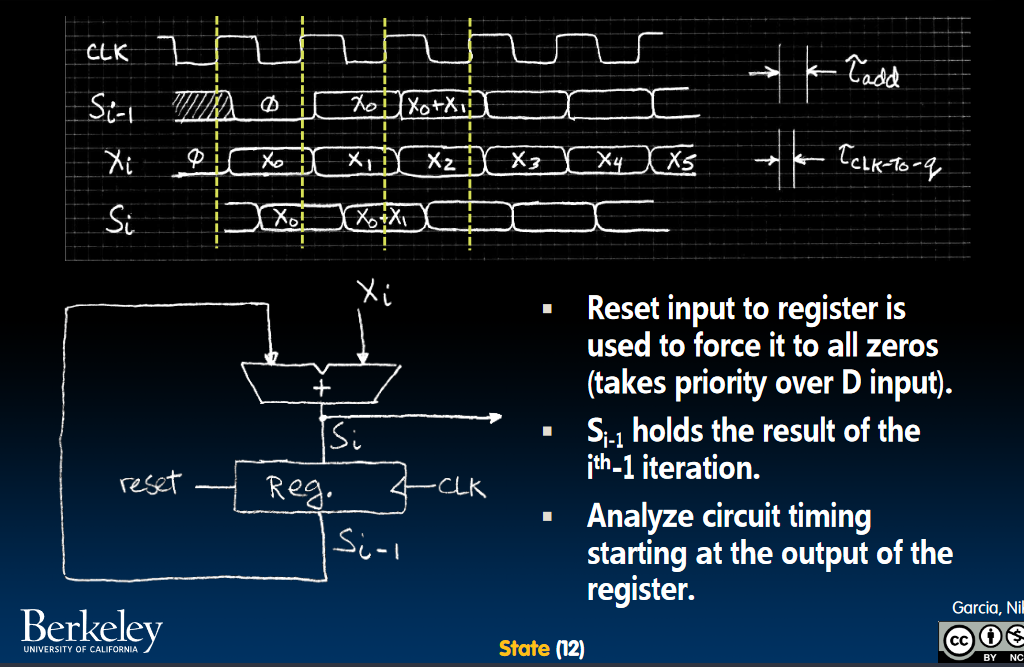

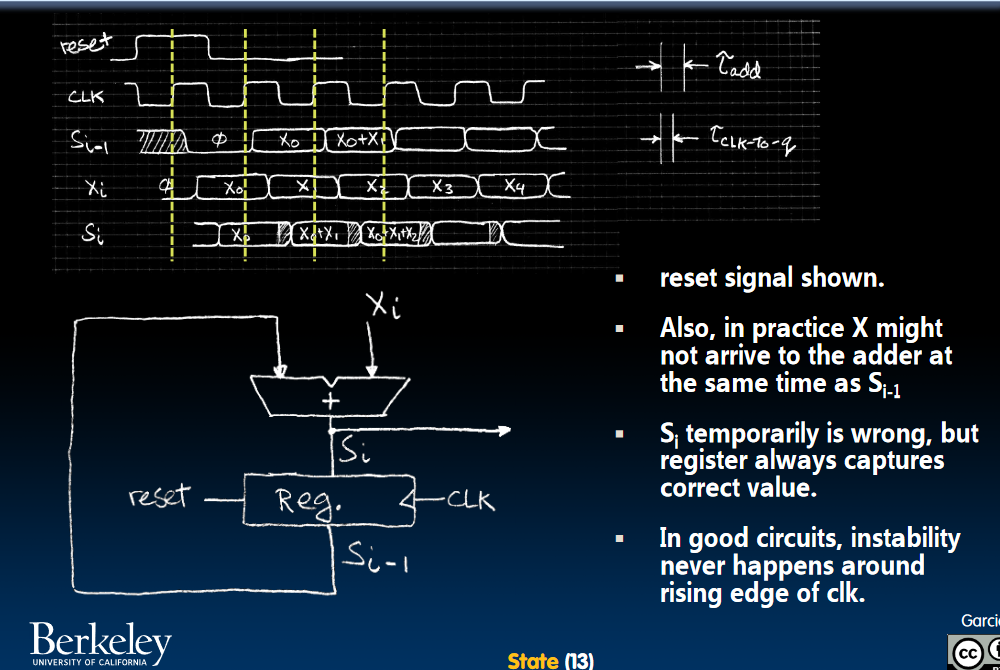

以触发器时序图角度再看累加器

- 寄存器的重置输入用于强迫寄存器到所有的零点(优先于D输入)。

- § Si - 1保存了第i - 1次迭代的结果。

- §从寄存器的输出开始分析电路时序。

- Si暂时是错误的,但寄存器总是捕获正确的值。

- 在好的电路中,clk上升沿附近不会出现不稳定现象。

这个图需要注意的是Si-1是输入,Si才是输出

简述下全过程:

- reset开关启动,Si-1设置为0,同Xi一起进入加法器中,Si再经过寄存器变成Si-1同Xi进行计算

使用流水线/管线设计来提高系统的性能(Pipelining for Performance)

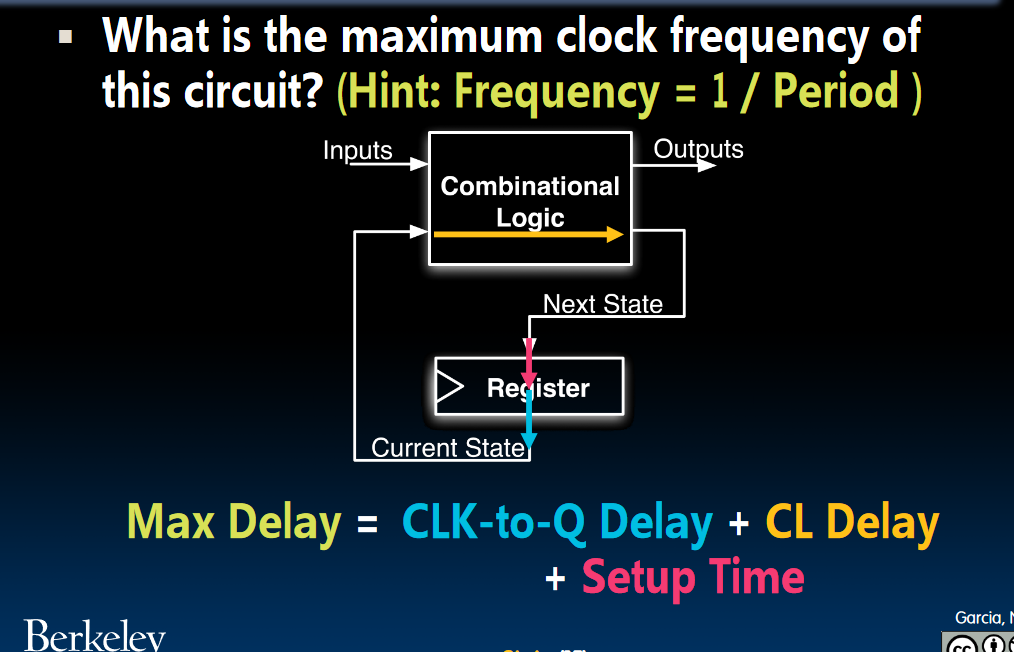

最大时钟频率

- 讨论了如何减少周期以提高频率。

- 通过电路的延迟分析标准电路,得出第一个延迟是时钟到Q的时间(t_clk_to_Q),第二个延迟是CL Delay组合逻辑延迟,第三是因为在t_setup之前即在下一上升时cl需要保持稳定

- 重点在于确保下一个上升沿之前的所有延迟都稳定。

图中路线颜色对应时间颜色

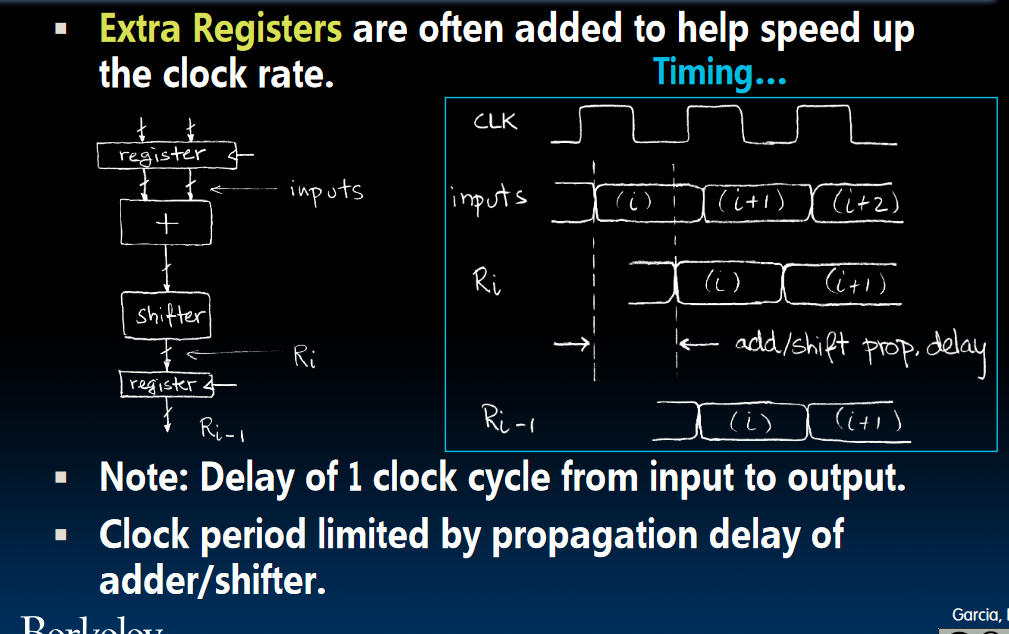

流水线的概念

- 将复杂的任务分割成更小的步骤,以提高处理频率。

- 通过一个例子解释:想象一个生产线上包裹巧克力和写俳句的任务,若分给两个人完成,每一步都会更快。

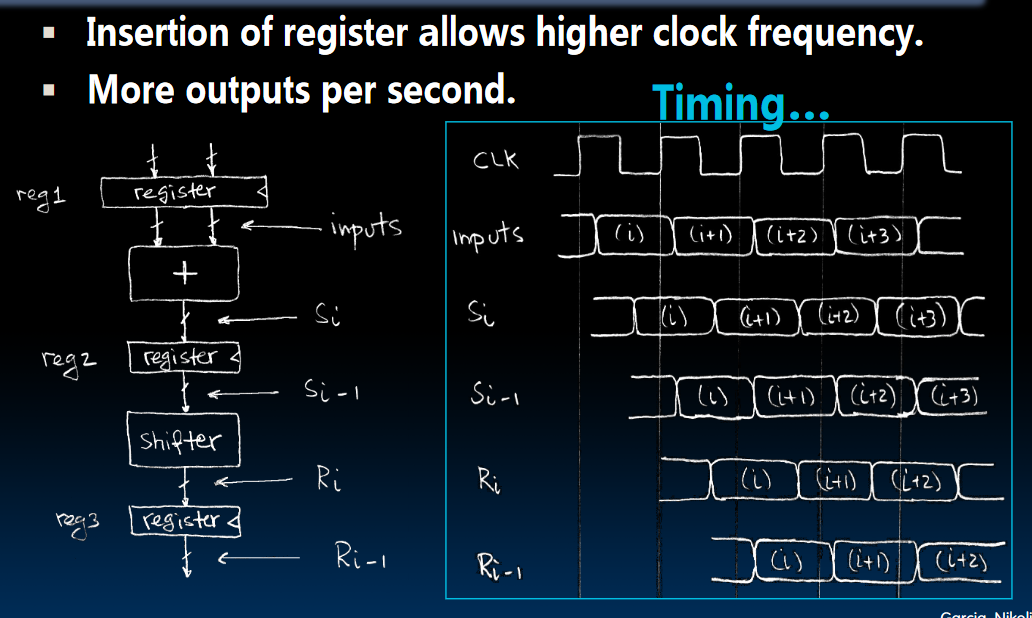

- 插入更多寄存器来分割任务,从而减少每个步骤的延迟。

实现流水线

- 在组合逻辑电路中插入额外的寄存器。

- 时钟上升沿到输出稳定之间的延迟称为t_clk_to_Q。

- 分割后的每个步骤的延迟更小,整体处理频率更高。

是在+和shifter中间加了个reg后相当于把CL delay拆开成两个独立的这个数据回路,所以最大延迟减小了时钟周期小了,时钟频率就大了,output就多了。

代价与收益

- 流水线使每秒的输出更多,但每个数据通过流水线所需的时间略长。

- 这种方法的整体收益是每秒处理更多的数据。

关键术语回顾

- 时钟:系统的心跳。

- 设置时间(Setup Time):上升沿之前数据必须稳定的时间。

- 保持时间(Hold Time):上升沿之后数据必须保持稳定的时间。

- 时钟到Q的时间(t_clk_to_Q):上升沿发生到数据在输出端口稳定之间的延迟。

- 触发器:构建寄存器的基础,用于RISC V机器的数据路径。

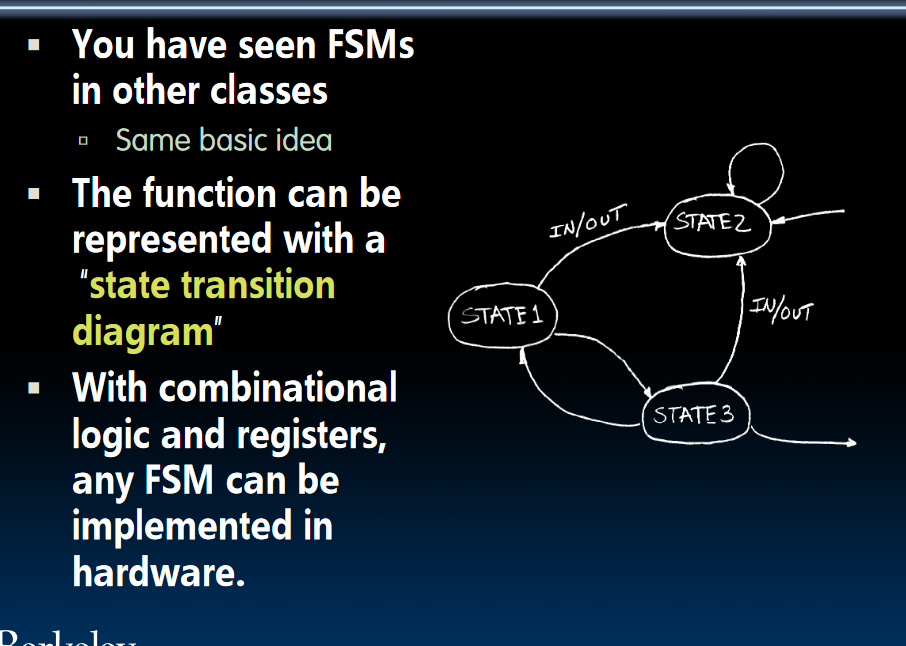

有限状态机(Finite State Machines)

有限状态机的基本概念

- 状态与转换:FSM由一系列状态和转换组成,箭头表示转换。

- 输出的来源:输出可以是转换的函数,也可以附加在状态上。

- 转换条件:每个状态都必须有所有可能输入的出口箭头。

- 初始状态:每个FSM需要有一个箭头指示初始状态或用双圈标示初始状态。

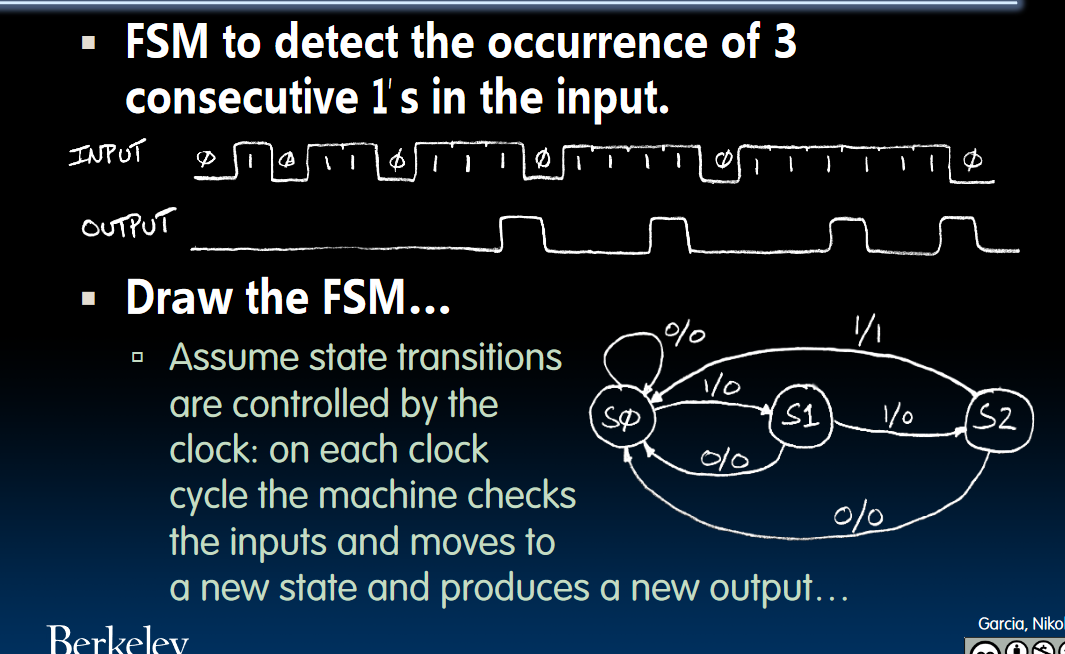

实例:检测三个连续的1

FSM可以用来检测输入序列中的特定模式。以下是一个简单的例子,用于检测三个连续的1。

状态机设计

- 状态表示:

状态0:初始化状态,表示没有检测到1。状态1:检测到一个1。状态2:检测到两个连续的1。状态0:重新回到初始状态,表示检测到三个连续的1。

状态转换规则

- 状态0:

- 输入0:保持在状态0。

- 输入1:转换到状态1。

- 状态1:

- 输入0:回到状态0。

- 输入1:转换到状态2。

- 状态2:

- 输入0:回到状态0。

- 输入1:输出1,表示检测到三个连续的1,然后回到状态0。

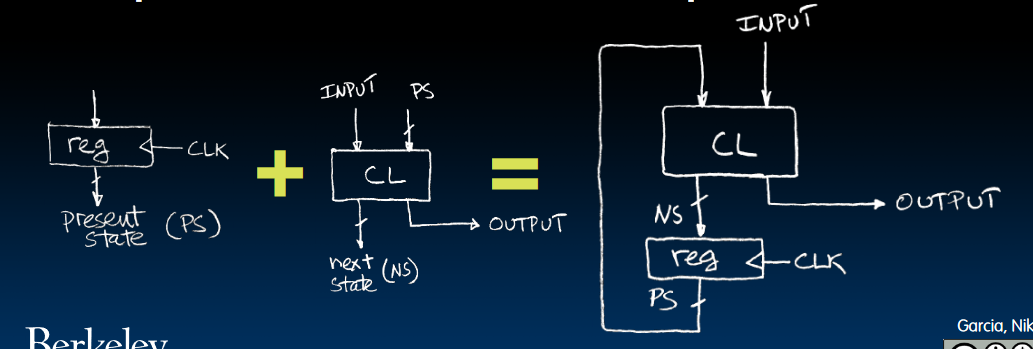

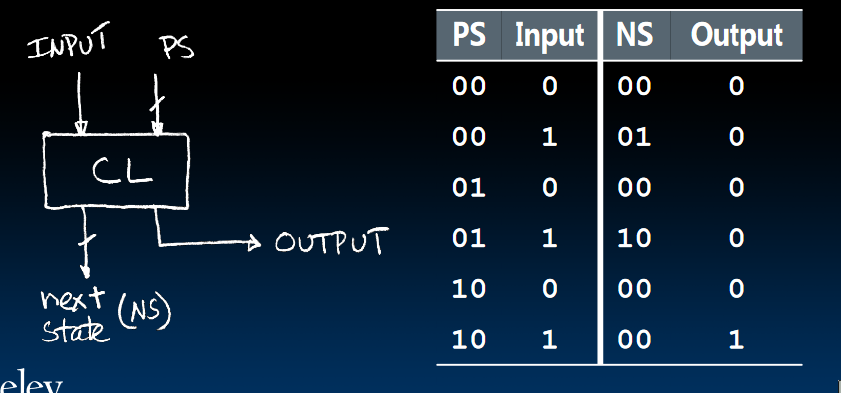

FSM的硬件实现

- ..因此需要一个寄存器来保存机器处于哪个状态的表示。

- ú为每个状态使用唯一的位模式。

- 使用组合逻辑电路实现一个函数,将输入和当前状态( PS )的输入映射到下一个状态( NS )和输出。

FSM的硬件:组合逻辑

下篇详讲

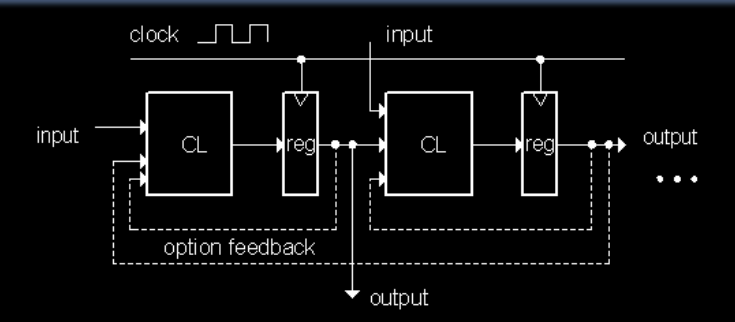

同步系统的一般模型

- 由寄存器分隔的CL块集合。

- 寄存器可以背靠背,CL块可以背靠背。

- 反馈是可选的。

- 时钟信号只与寄存器的时钟输入连接。

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 云泥小窝!

评论