12-CS61C学习笔记-Pipelining

6个计算机体系结构的伟大思想

抽象(表示/解释的层次)

摩尔定律

局部性原理/内存层次结构

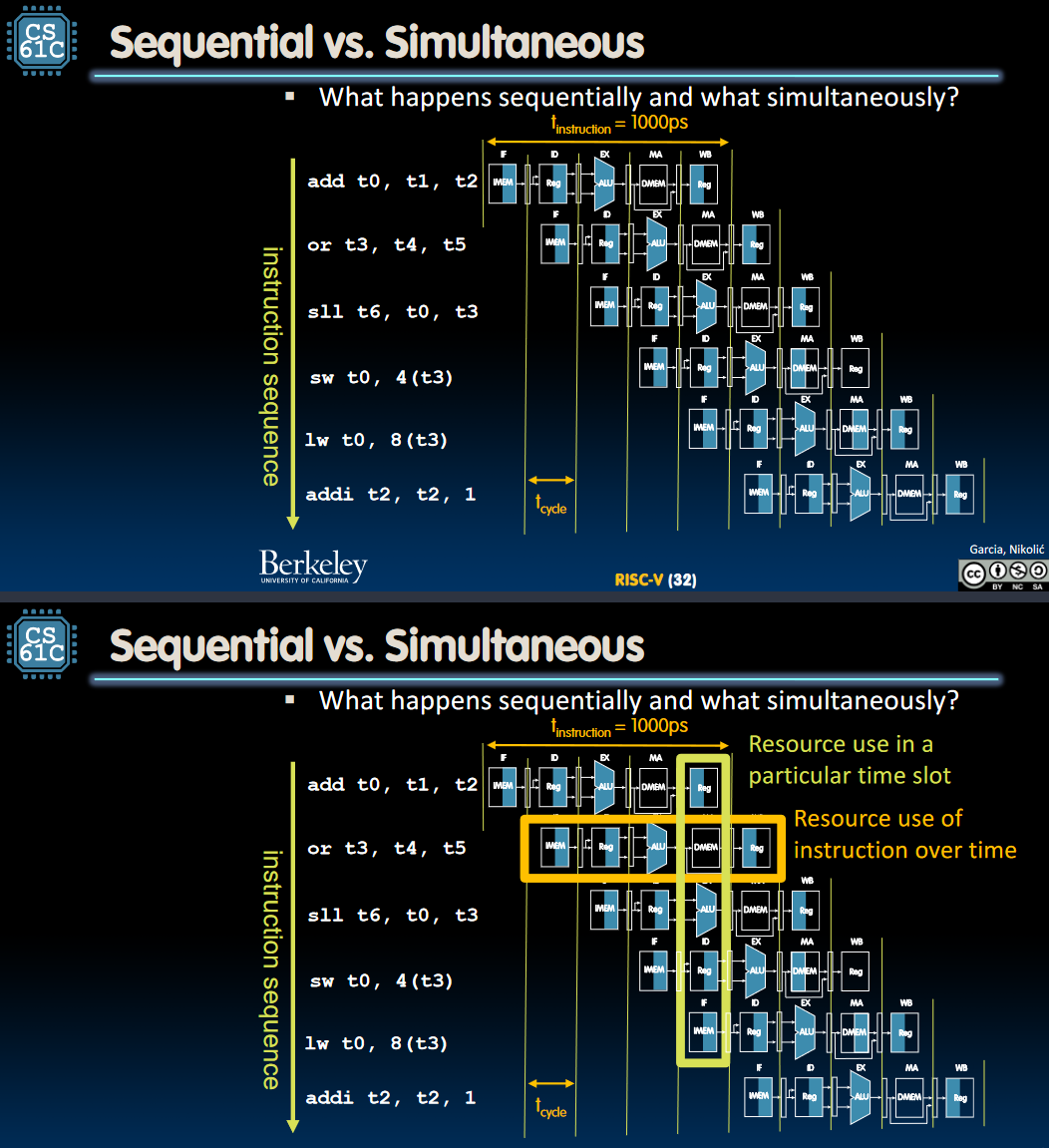

并行性

性能测量与改进

冗余实现的可靠性

1. 抽象(Abstraction:Layers of Representation/Interpretation)

抽象是将复杂的系统分解为更简单的、可管理的层次,每一层对上层提供简化的接口。计算机体系结构中,硬件和软件的各个层次(例如电路、逻辑门、指令集、操作系统等)都是通过抽象来彼此分离的。这使得开发者可以在特定的层次上工作,而不用了解底层的细节。

2. 摩尔定律(Moore’s Law)

摩尔定律是由英特尔联合创始人戈登·摩尔提出的,指出每隔约18到24个月,集成电路上可容纳的晶体管数量就会翻倍,导致计算能力的快速增长。虽然这一趋势在最近几年有所减缓,但它仍然是现代计算机体系结构发展中最重要的推动力之一。

3. 局部性原理/内存层次结构(Principle of Locality/Memory Hierarchy)

局部性原理表示程序和数据的访问行为具有空间和时间上的局部性,即访问某一位置的内存后,接下来很可能会访问其附近的内存位置。基于这一原理,计算机内存系统被设计为层次结构,如寄存器、缓存、主存和硬盘等,以平衡速度和成本。利用缓存可以显著提高系统性能。

4. 并行性(Parallelism)

并行性是指通过同时执行多个任务来提高性能。现代计算机系统中的多核处理器、图形处理单元(GPU)等都利用并行性来提高计算能力。并行性可以存在于不同层次,例如指令级并行、线程级并行和数据级并行等。

5. 性能测量与改进(Performance Measurement & Improvement)

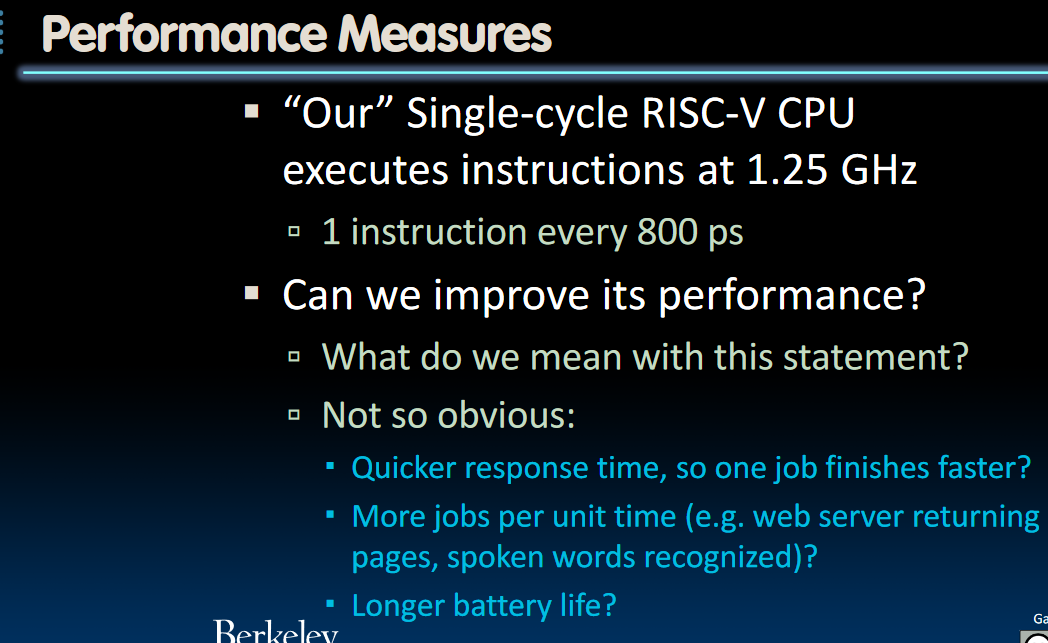

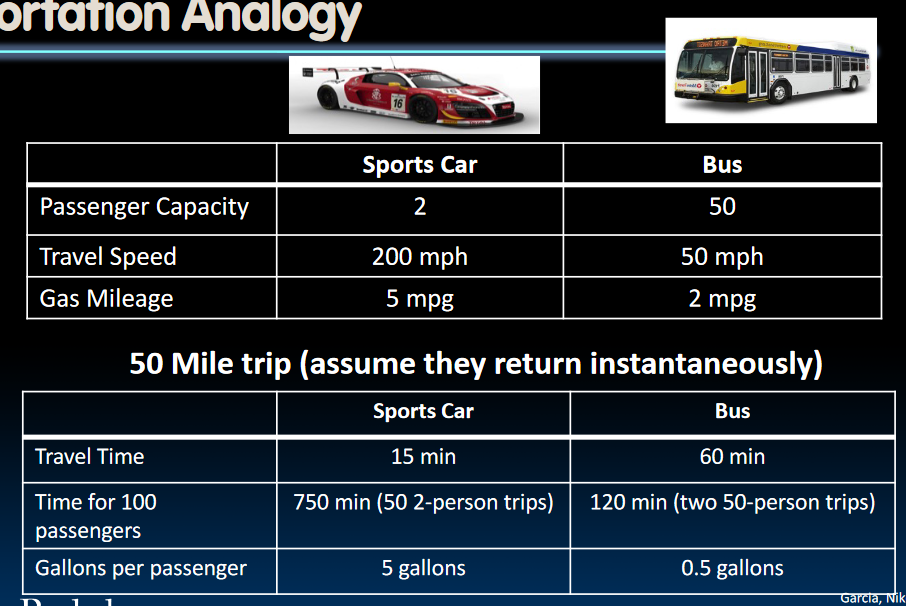

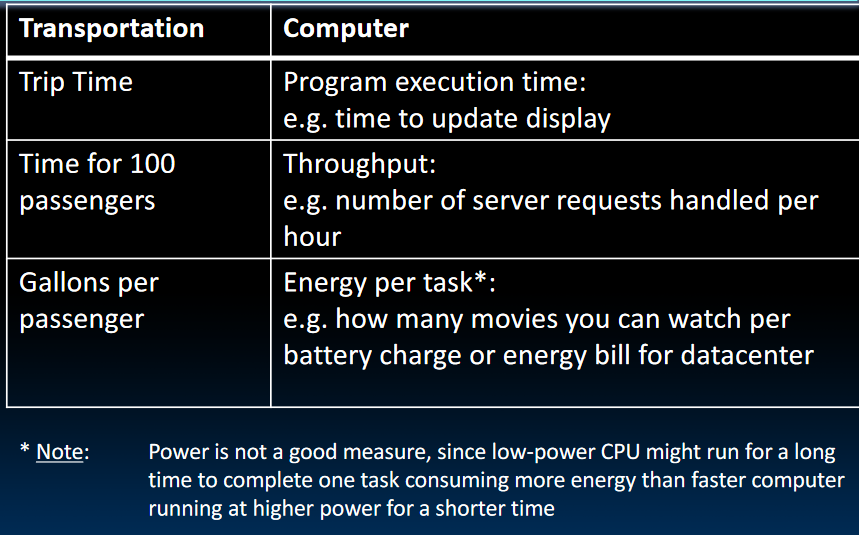

衡量系统性能是设计和优化计算机体系结构的重要部分,常用的性能指标包括指令每秒执行数(IPS)、延迟、吞吐量等。通过这些指标,设计者可以识别系统瓶颈并进行优化,例如通过更高效的指令集设计、硬件优化、编译器优化等提高性能。

6. 冗余实现的可靠性(Dependability via Redundancy)

为了确保系统的可靠性,尤其是在关键任务应用中,设计者往往通过冗余来提高容错能力。冗余可以在硬件、软件或数据层面进行,例如冗余硬盘阵列(RAID)、错误检测与纠正码(ECC)等。通过引入冗余,即便某些组件出现故障,系统依然能够继续正常运行。

让我们集中在第5个思想:Performance Measurement & Improvement

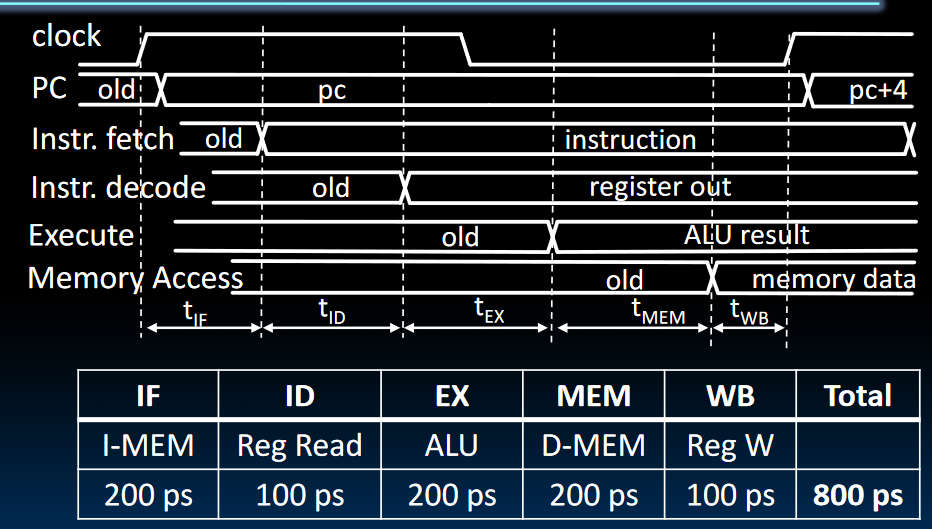

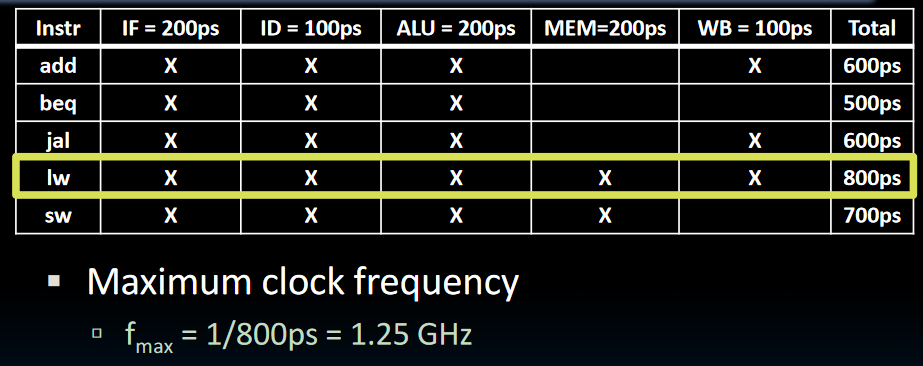

Instruction Timing

交通工具模拟

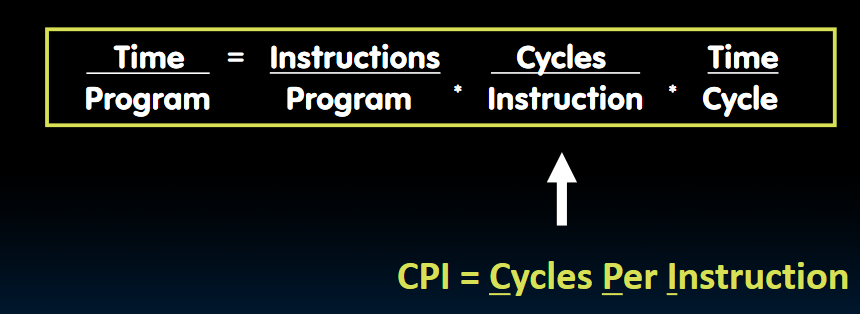

处理器性能铁律

Instructions per Program

由以下决定:

- 任务

- 算法

- 编程语言

- 编译程序

- 指令集架构Instruction Set Architecture( ISA )

CPI(Average) Clock Cycle per Instruction

由以下决定:

- 指令集架构Instruction Set Architecture( ISA )

- 处理器实现(或微体系结构)

- E.g. for “our” single-cycle RISC-V design, CPI = 1

- 复杂指令(如strcpy ),CPI > > 1

- 超标量处理器(Superscalar processors),CPI < 1

Time per Cycle(1/Frequency)

由以下决定:

- 处理器微架构(通过逻辑门确定关键路径)

- 技术(例如5nm和28nm)

- 功率预算(低电压降低了晶体管的速度)

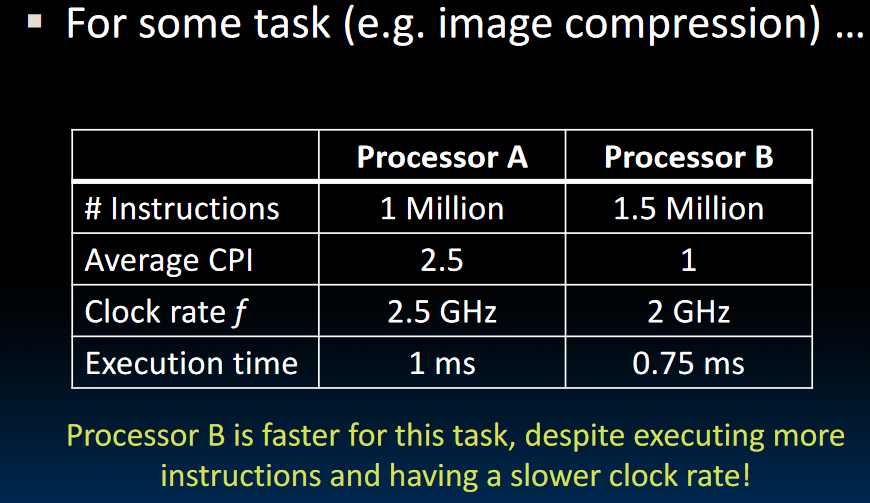

速度权衡(Speed Tradeoff)示例

关键在于CPI

哎这个后面不想写,以后用到了再整理

Pipelining

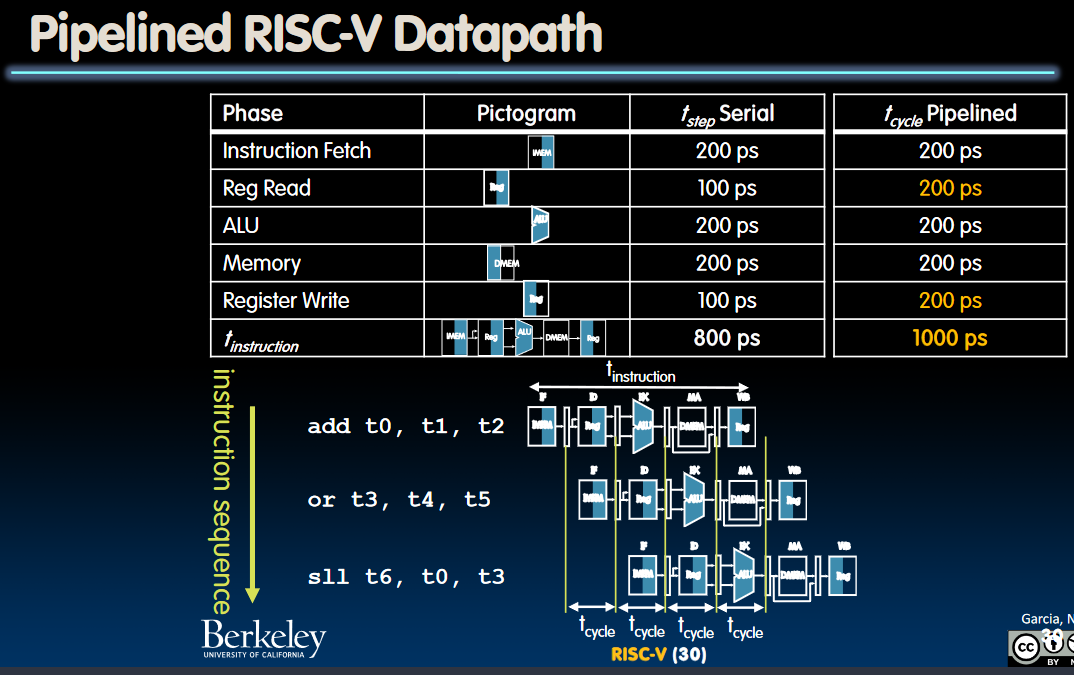

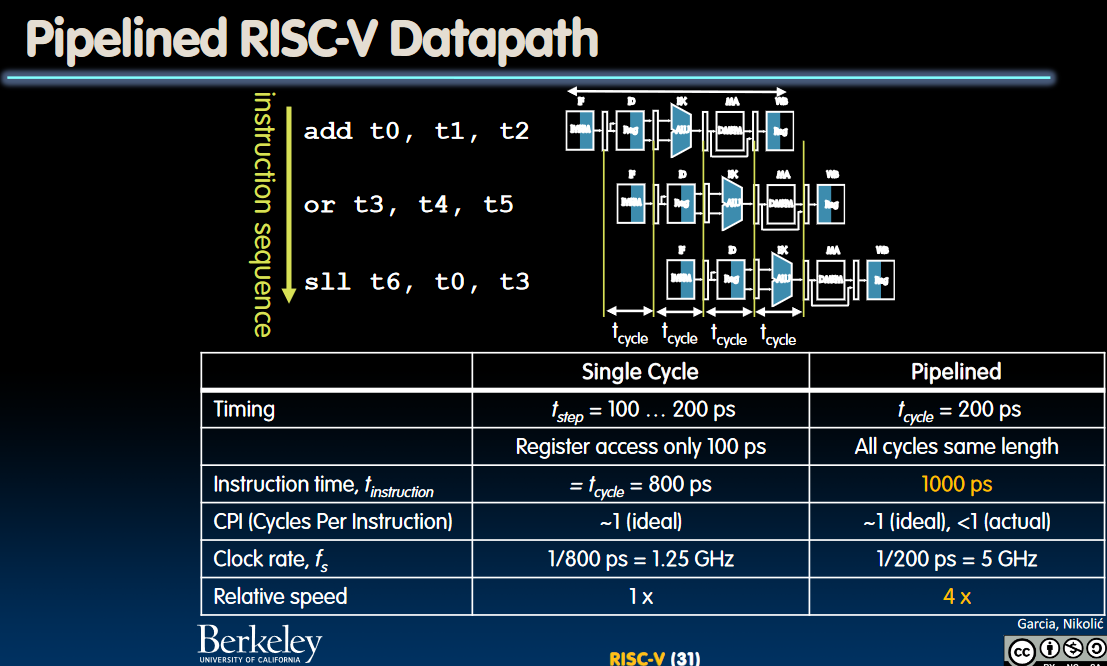

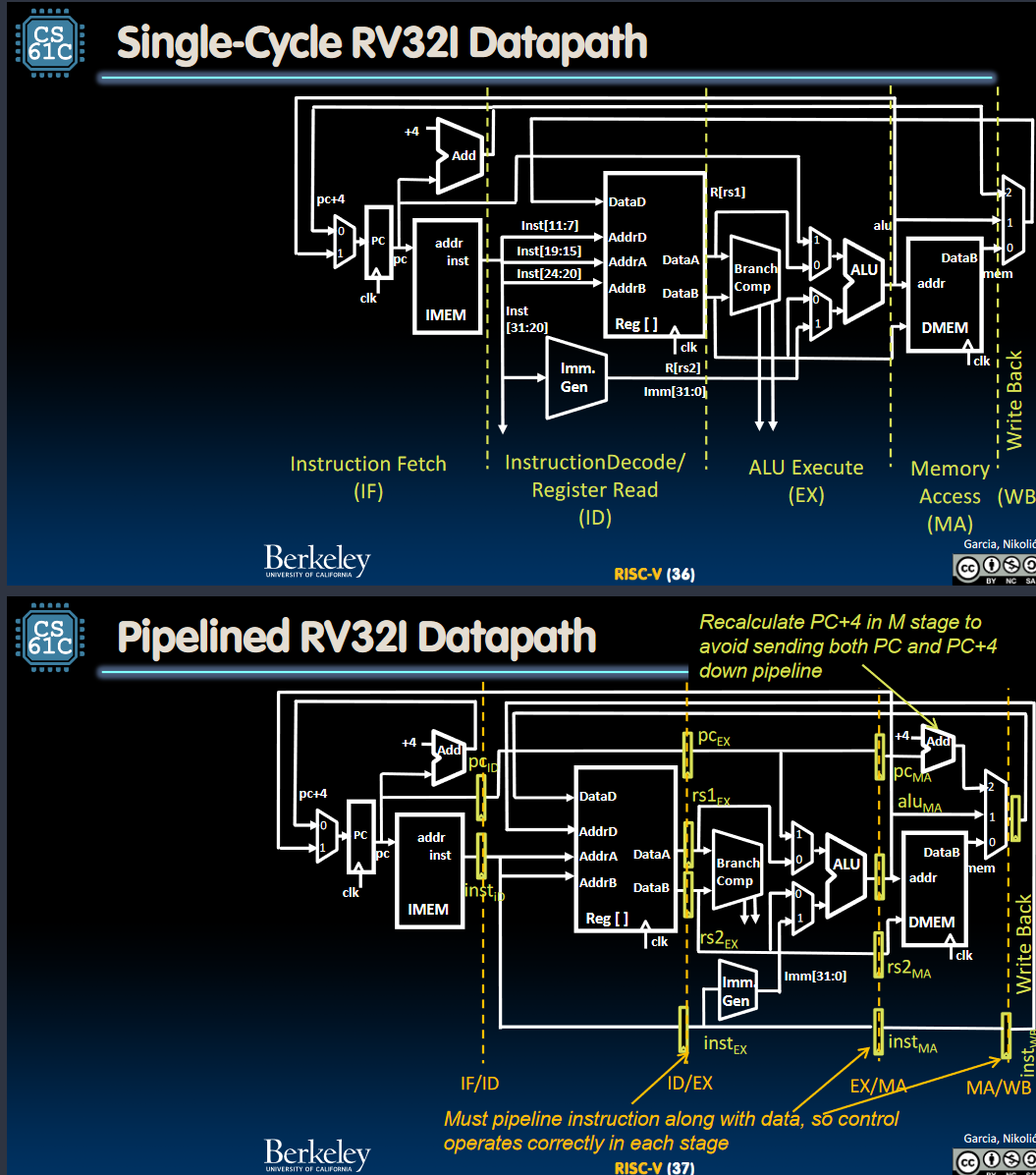

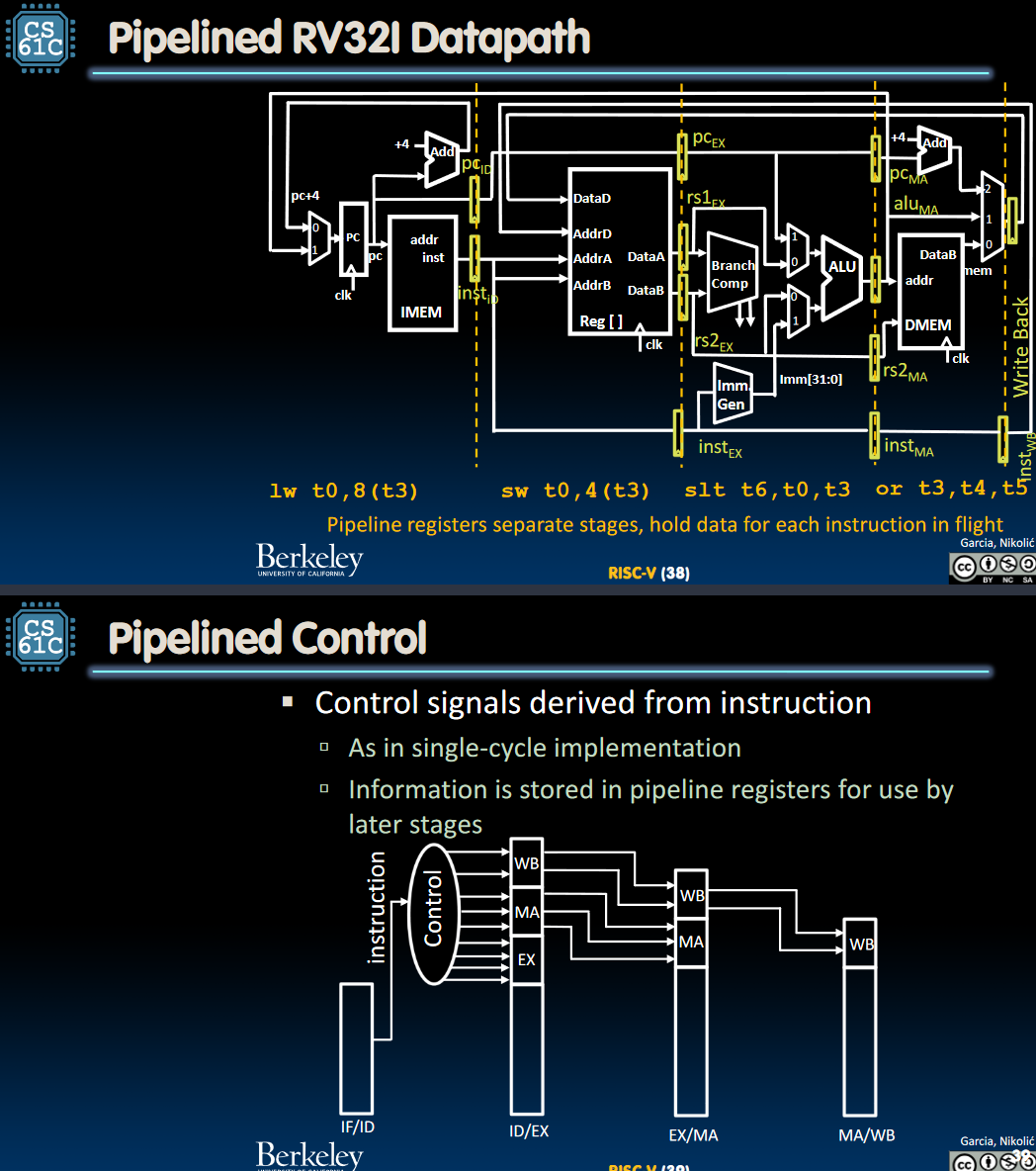

Pipelining Datapath

Pipeline Hazards

危险是在下一个时钟周期中阻止启动下一条指令的情况

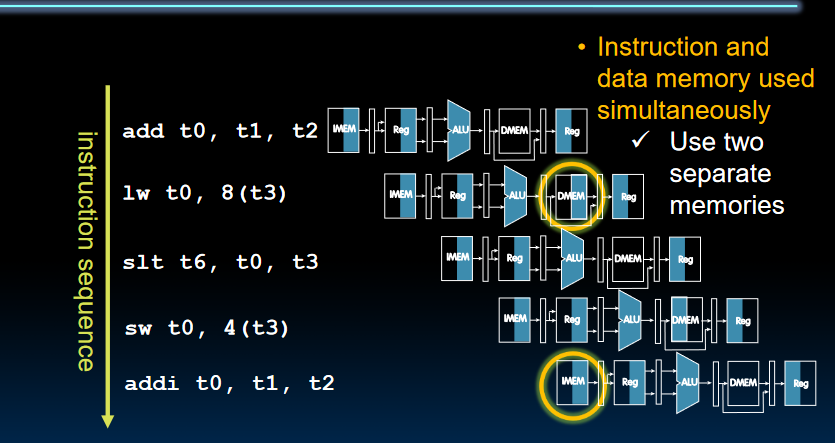

Structural hazard

- 一个需要的资源是繁忙的( e.g.需要在多个阶段进行)

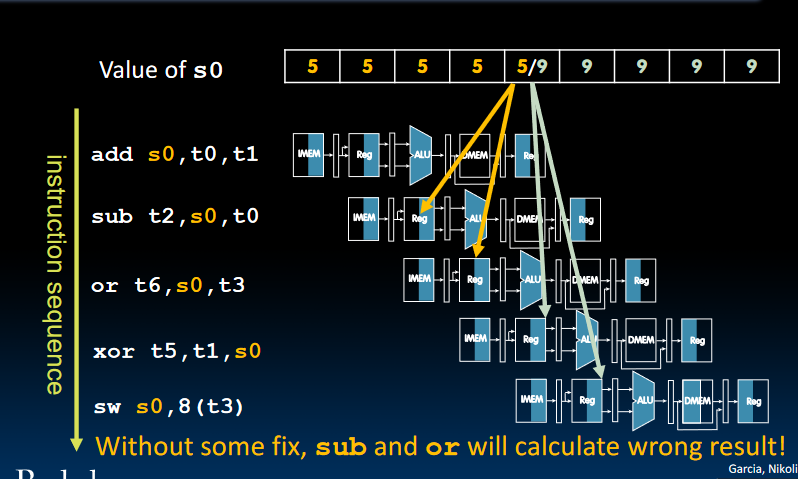

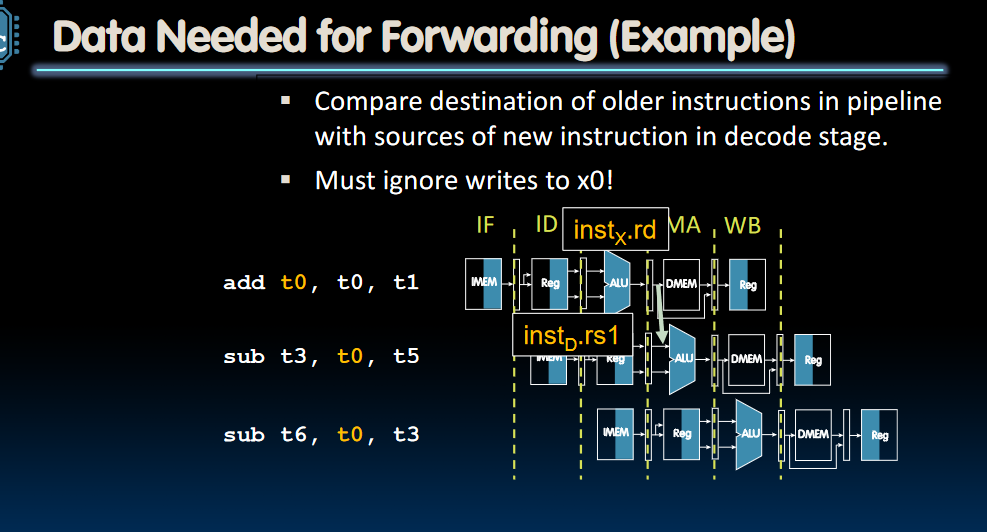

Data hazard

- 指令之间的数据依赖关系

- 需要等待之前的指令才能完成其数据读写方法

Control hazard

- 执行流程取决于先前的指令

- 问题:流水线中的两条或多条指令竞争访问单个物理资源

- 解决方案1:指令轮流使用资源,一些指令不得不停顿。

- 解决方案2:增加更多的硬件到机器中,可以通过增加更多的硬件来解决结构危险

Structural hazard

- 每条指令:

- 在解码阶段可以读到两个操作数

- 在写回阶段可以写一个值。

- 通过具有独立的”端口”来避免结构危险。

- 两个独立的读端口和一个独立的写端口

- 每个周期可以同时进行三次访问

Structural hazard: 内存访问

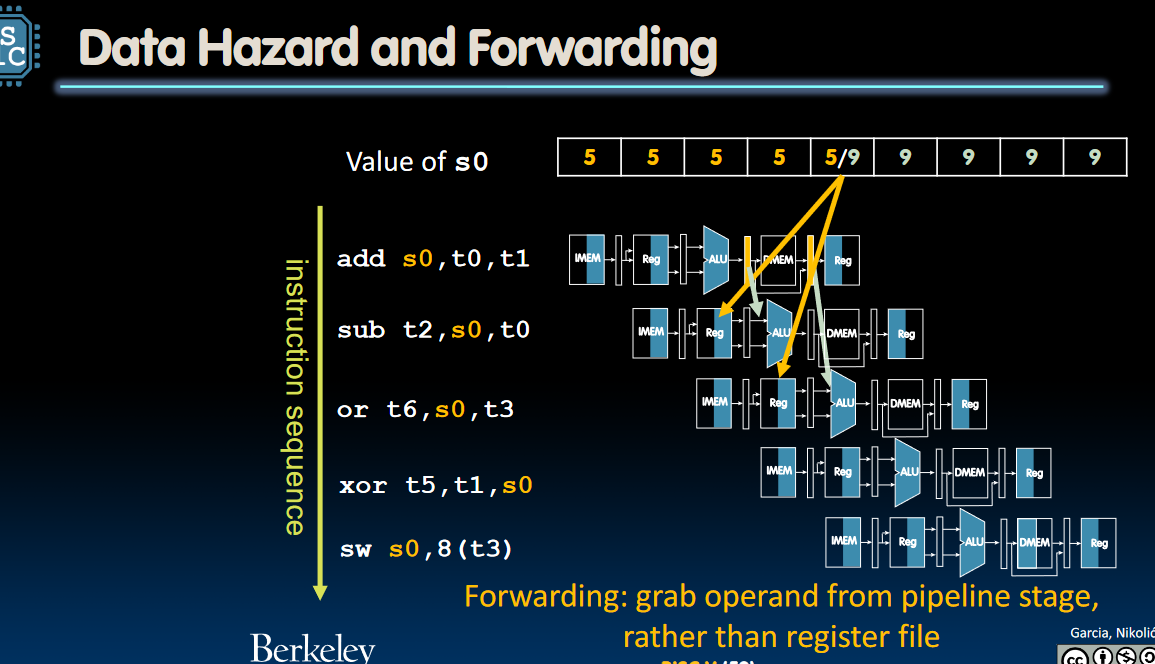

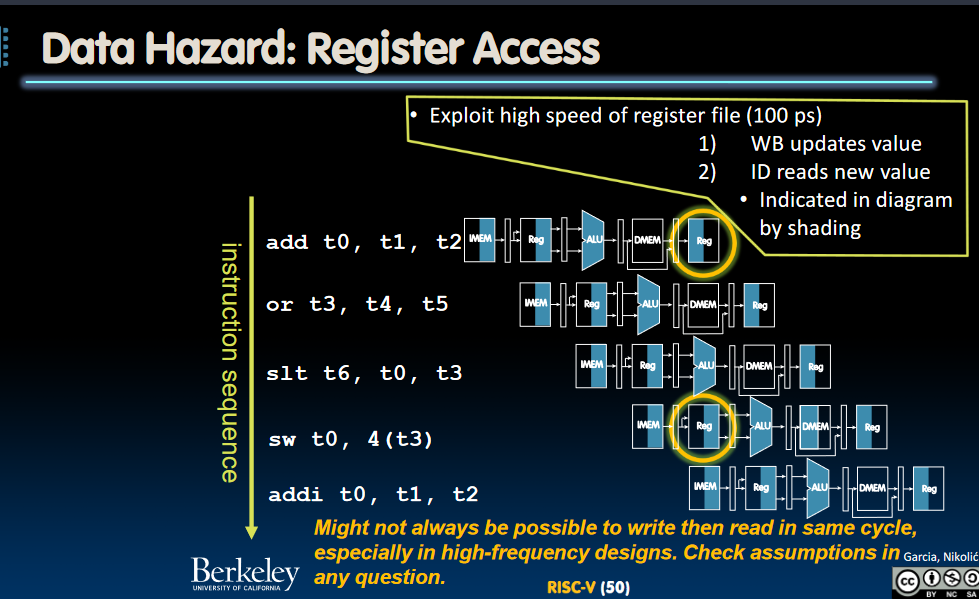

Data Hazards

寄存器访问

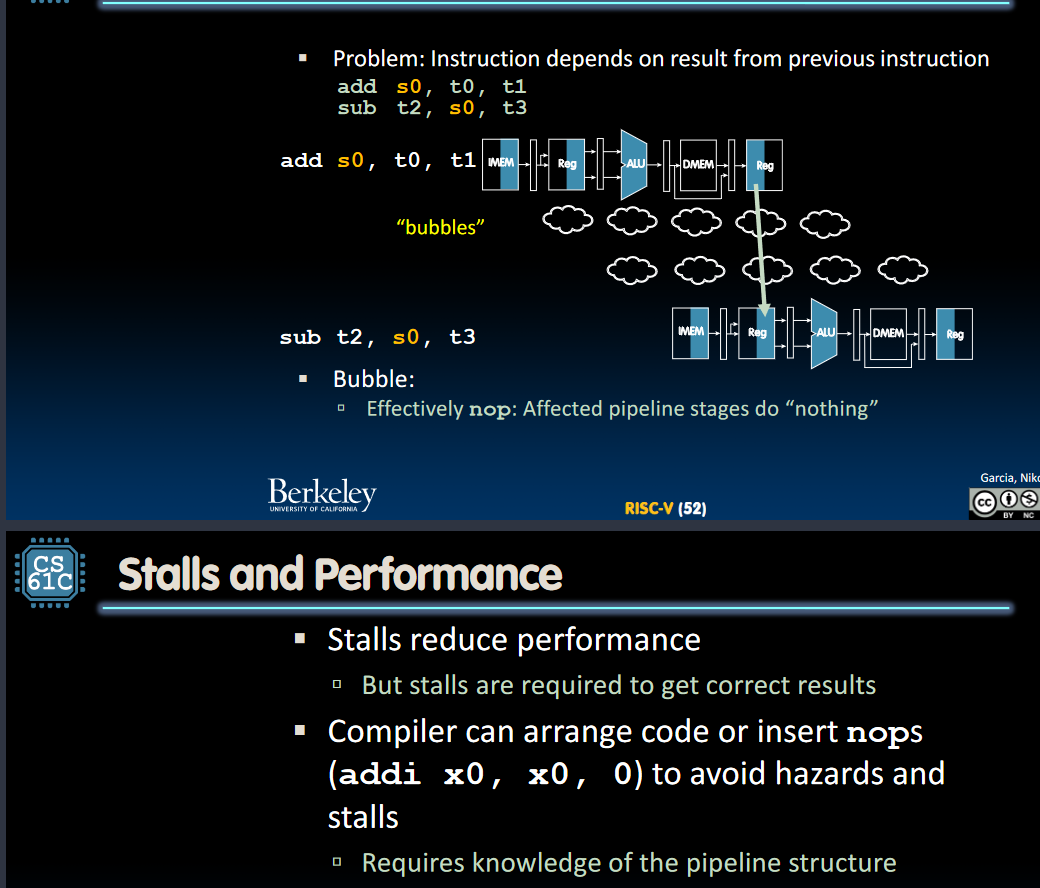

Solution 1: Stalling

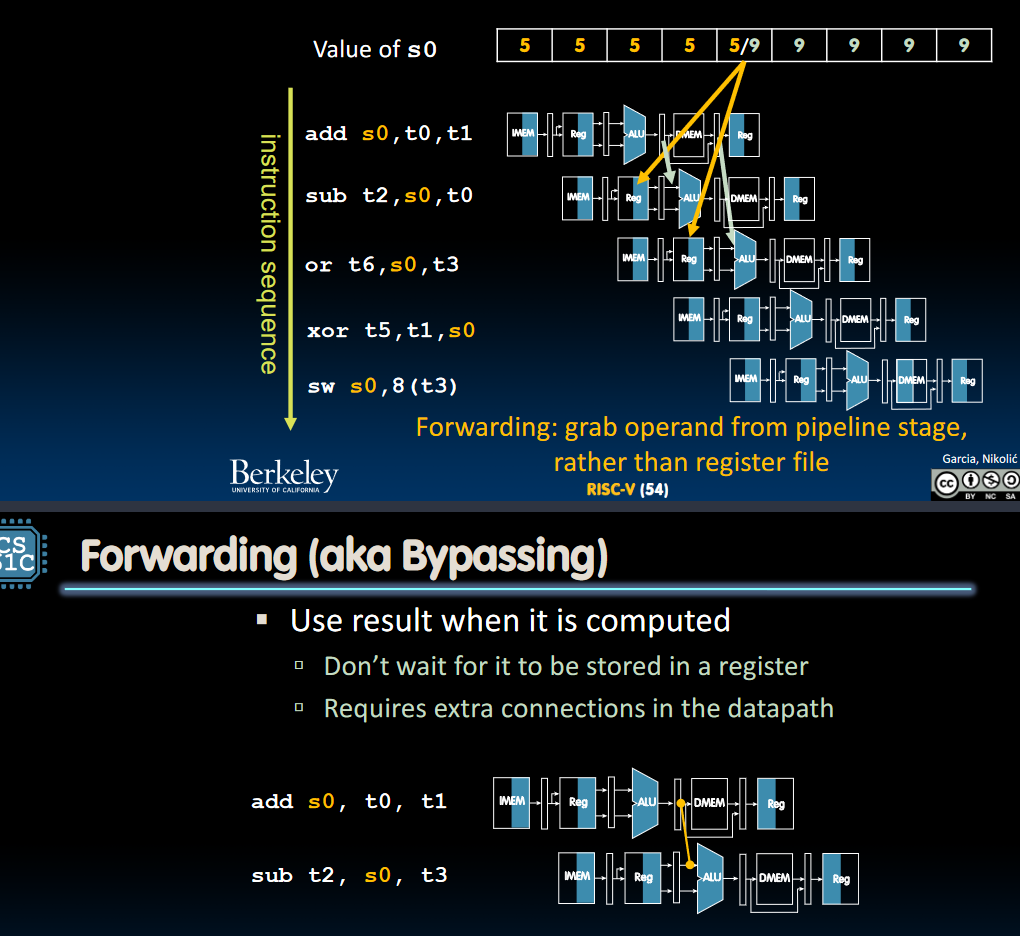

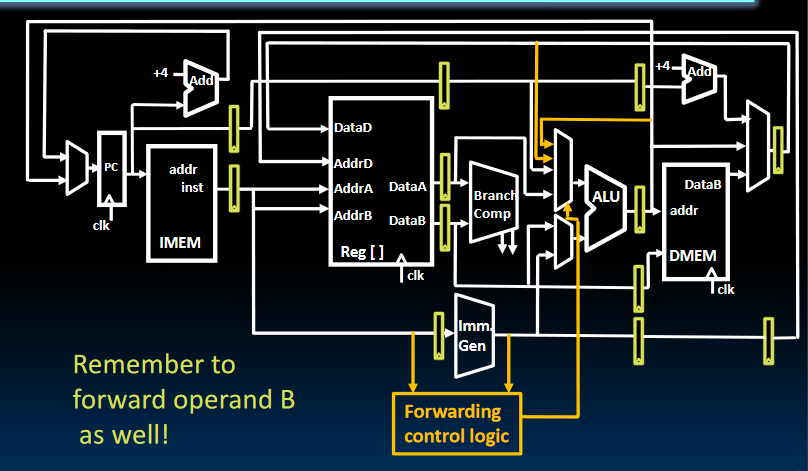

Solution 2: Forwarding

Pipelined RV32I Datapath

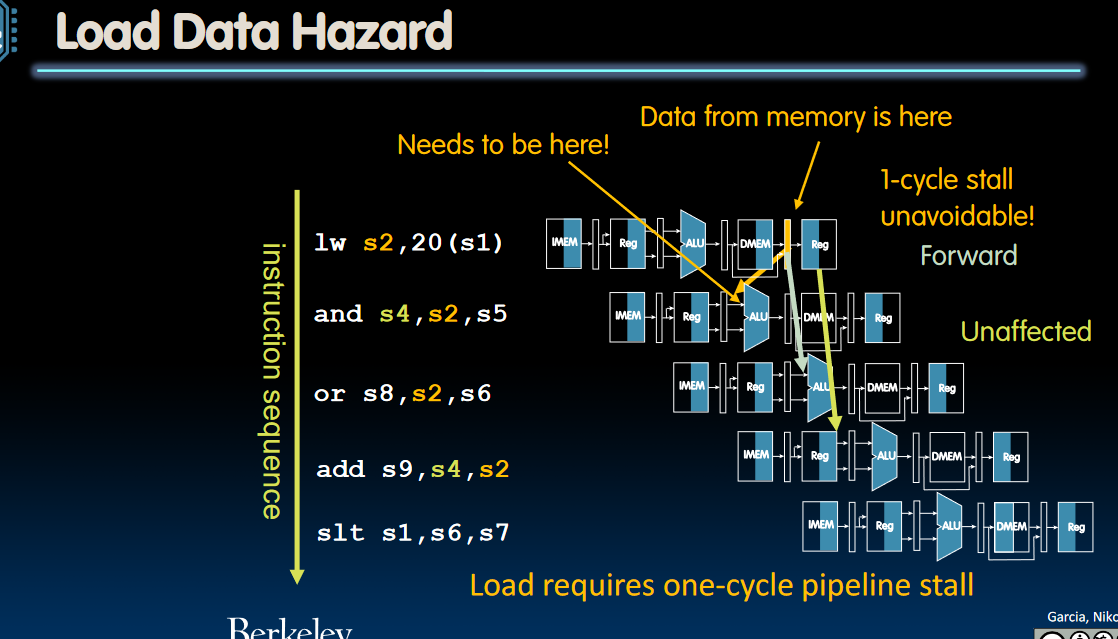

Load Data Hazard