CS61C学习笔记(六)-同步数字系统

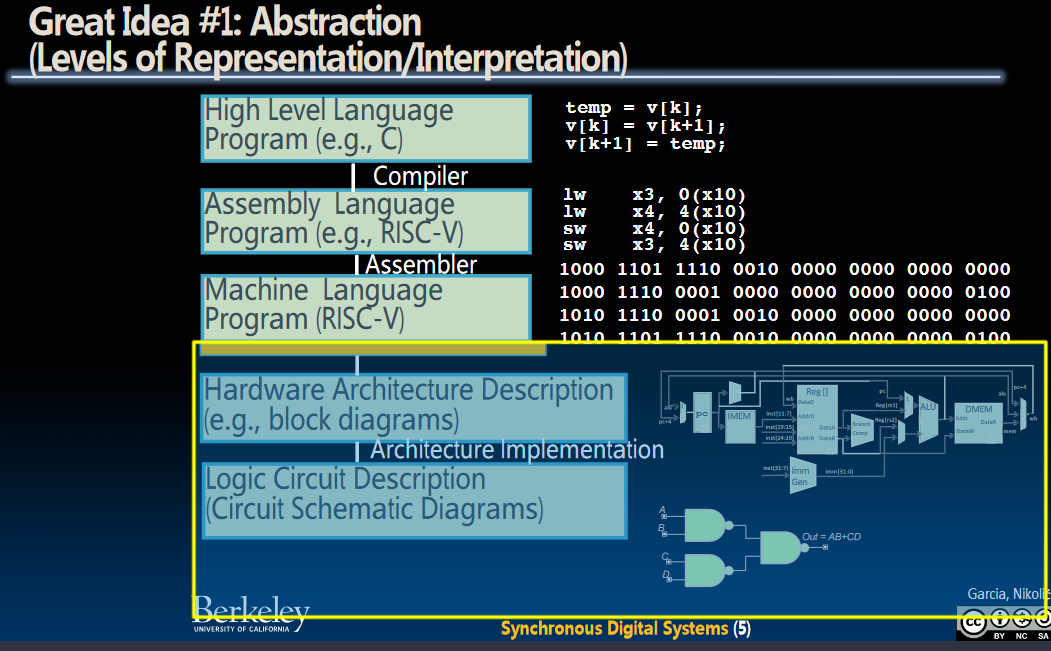

我们已经介绍了高级语言、汇编语言和机器语言,接下来我们从硬件架构和逻辑电路来讨论代码运行发生了什么

同步数字系统即Synchronous Digital Systems (SDS),接下来我们将讨论同步数字系统中的开关(Switches)、晶体管(Transistors)、信号(Signals)、波形(Waveforms)和状态(Status)

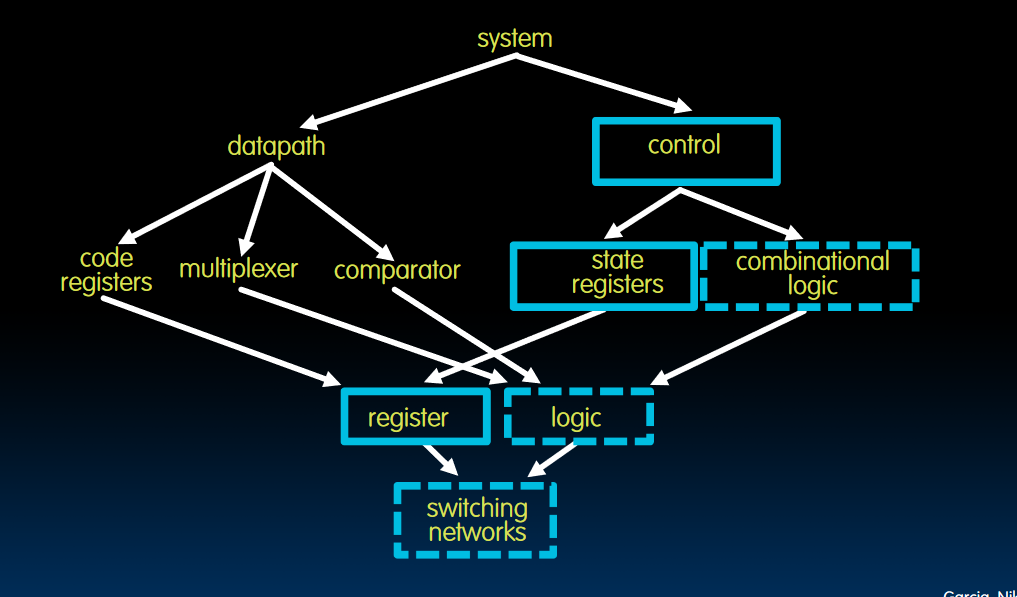

设计层次

同步数字系统

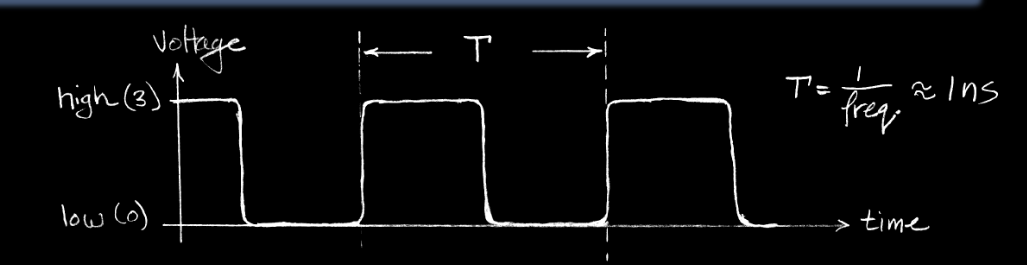

- 同步(Synchronous):系统有一个时钟信号(心跳),现代时钟频率通常在3到4 GHz范围内。

- 数字(Digital):

- 所有值都用离散值表示

- 将模拟电压和电流转换为数字信号(0和1)。

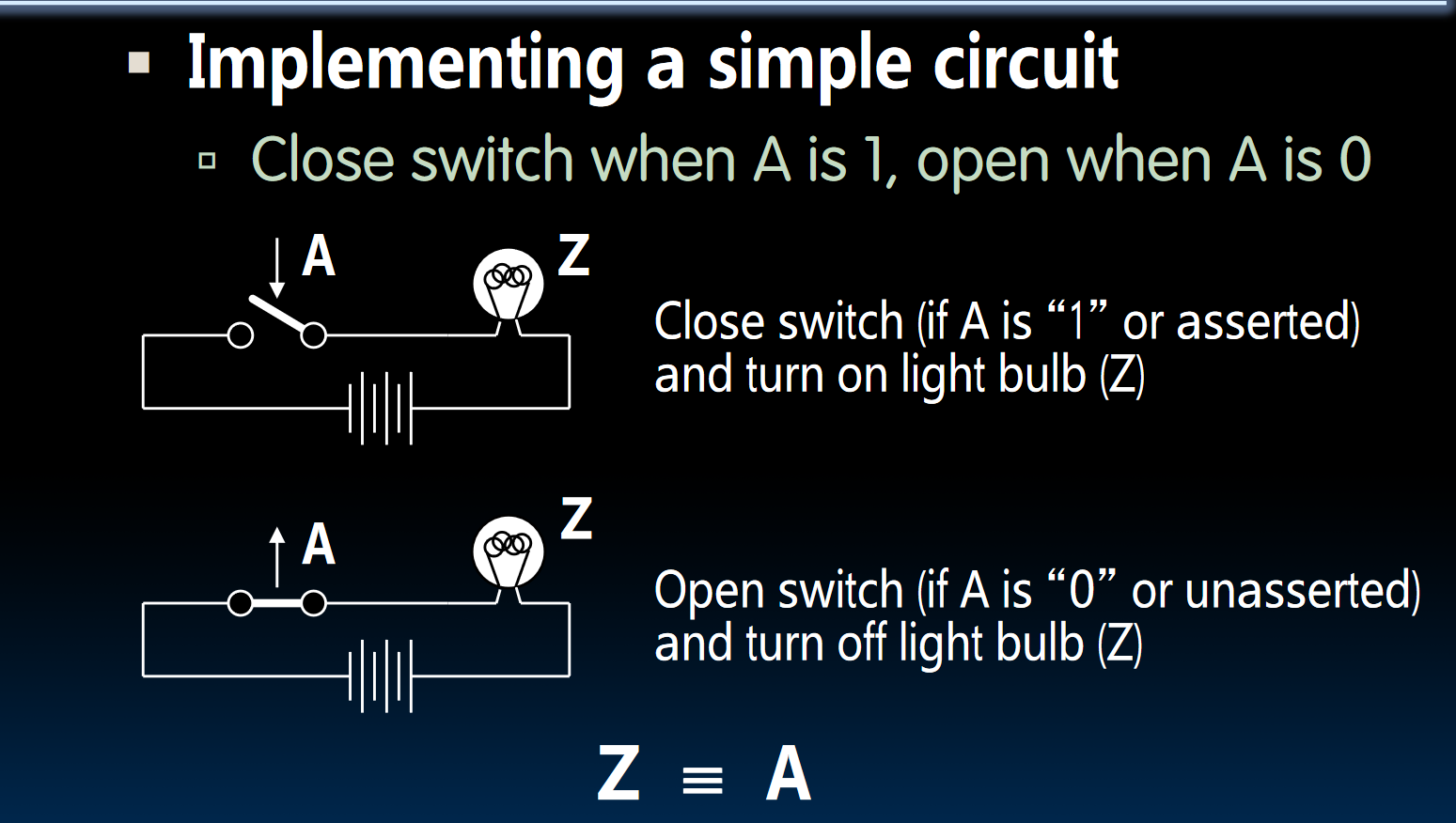

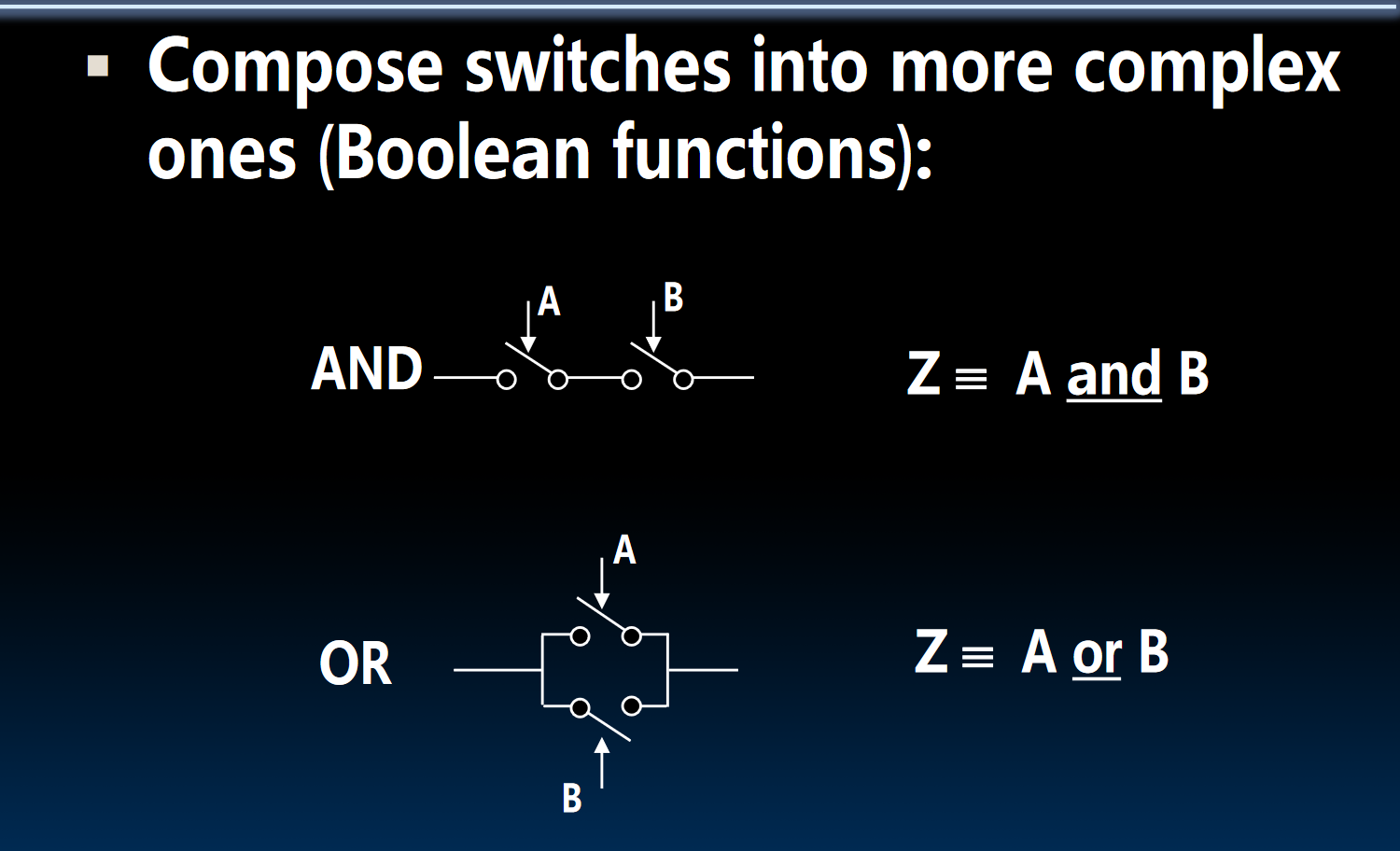

开关(Switches)

物理电路的基本要素

我们通常把闭合称为”断言(asserrte)”

晶体管(Transistor)

晶体管的基本概念

- 半导体:晶体管是半导体器件,有时导电,有时不导电。通过另一电源可以控制其导电性。

- 放大器与开关:晶体管既可用作放大器,也可用作开关。

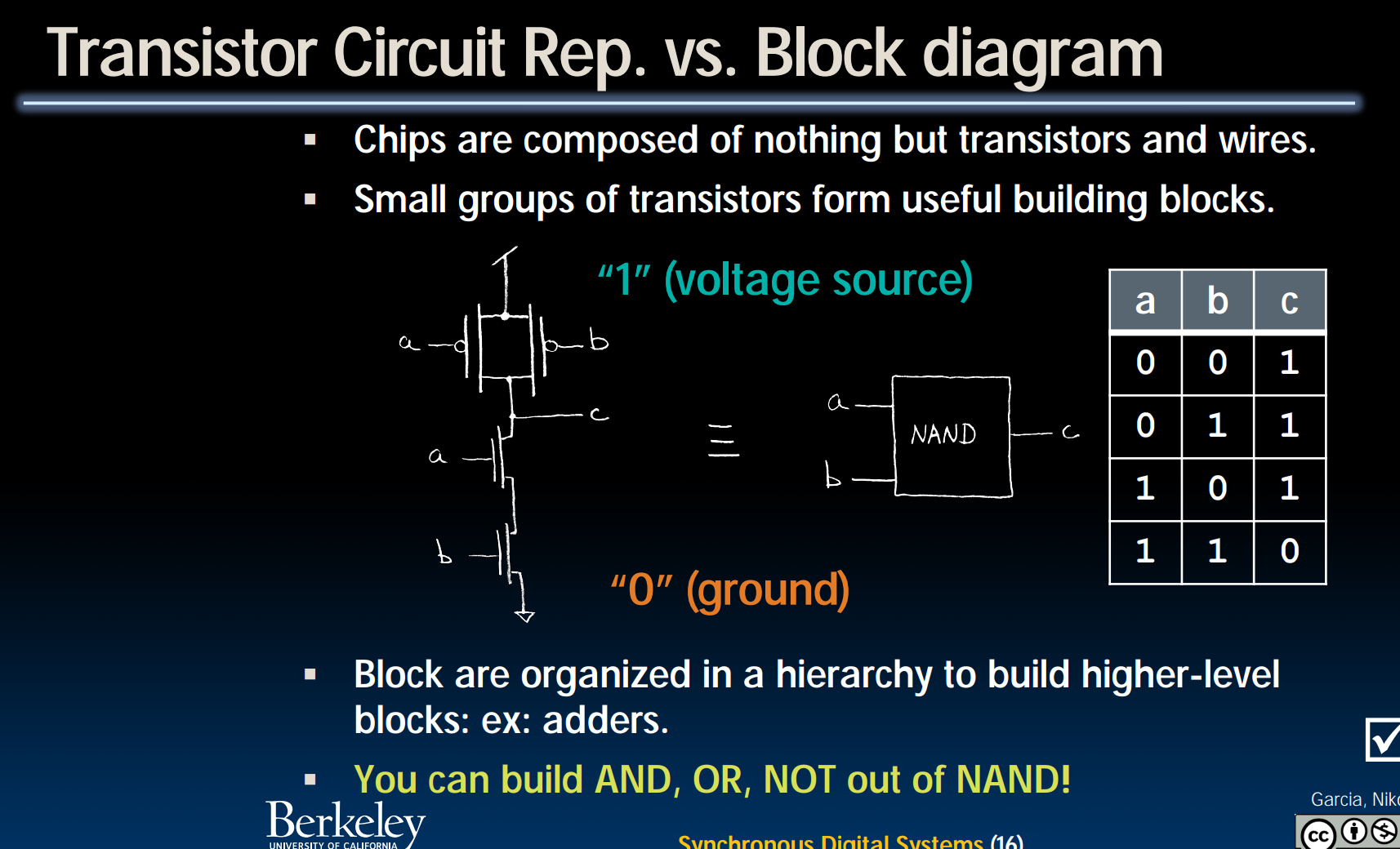

- CMOS技术:现代数字系统使用互补金属氧化物半导体(CMOS)技术,该技术使用电压控制开关。

- MOS: Metal-Oxide on Semiconductor 即 半导体上的金属-氧化物

- C为互补:常开和常闭的开关

晶体管的结构与工作原理

MOS管起电压控制开关的作用

三引脚器件:晶体管通常有三个引脚——漏极(Drain)、栅极(Gate)和源极(Source)。记住这三个名字的缩写DGS(Drain, Gate, Source)。

- 如何记忆?:Dan Garcia Says!

电压控制门:

- 栅极电压高于源极电压时,开关闭合,电流流动;

- 栅极电压低于源极电压时,开关断开,无电流流动。

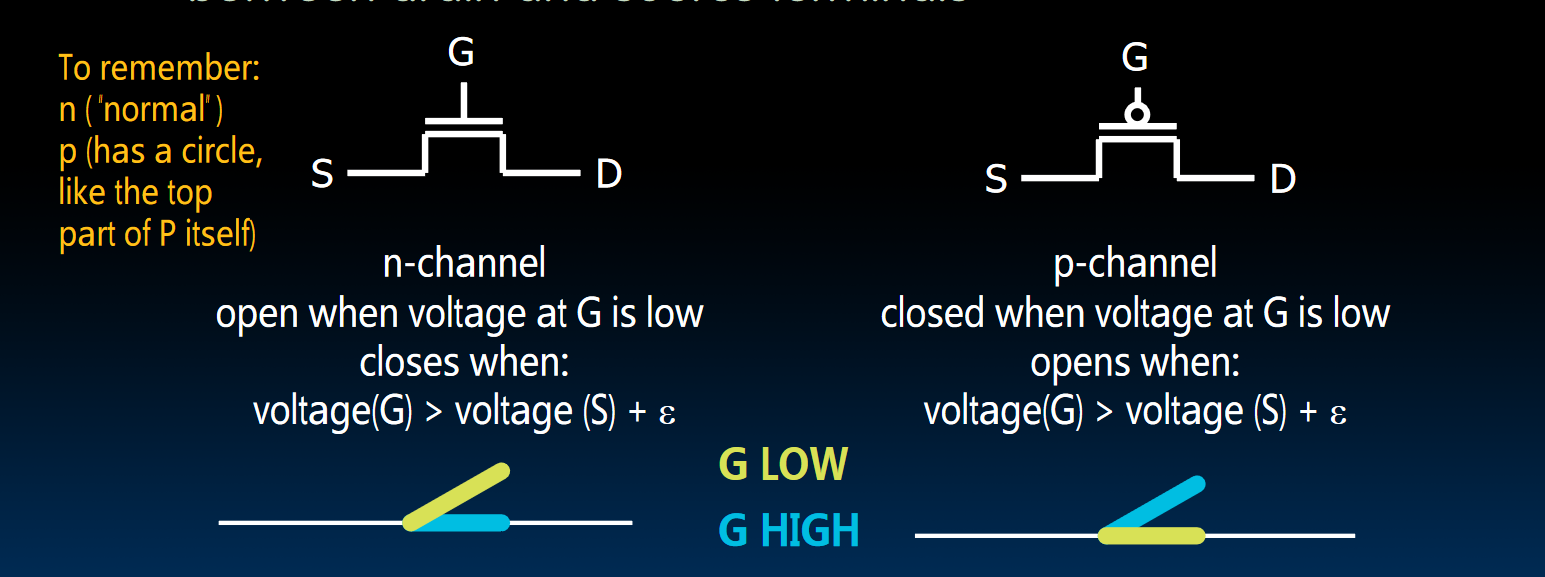

下图为N沟道与P沟道晶体管:

N沟道晶体管:栅极电压高于源极电压时开关闭合。

P沟道晶体管:栅极电压低于源极电压时开关闭合。

n’s the normal.

p’s the opposite.

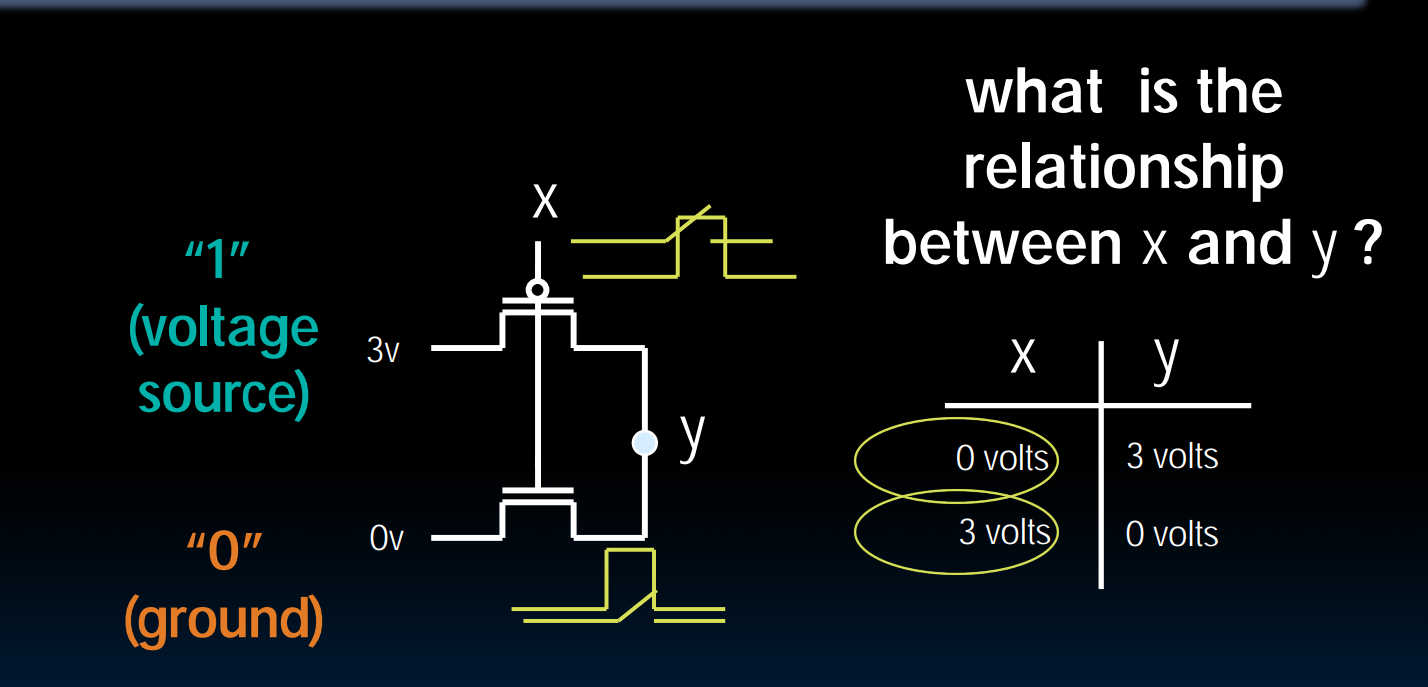

N/P沟道晶体管例子说明

对于这个电路图,有两个需要满足的要求:

- 我们总是必须让 y 有一个连接,要么到 0,要么到 3。

- 永远不能将 高电平对地、电源对地短路。 即电路中也不得存在 3 伏和 0 伏之间或 1到 0 之间的连接。

N/P沟道晶体管例子说明2

波形(Waveforms)和状态(Status)

Clocks

- 信号

- 当仅将数字处理为1或0时

- 通过导线连续传输

- 传输是有效即时的

- 暗示一条导线在某一时刻含有1个值

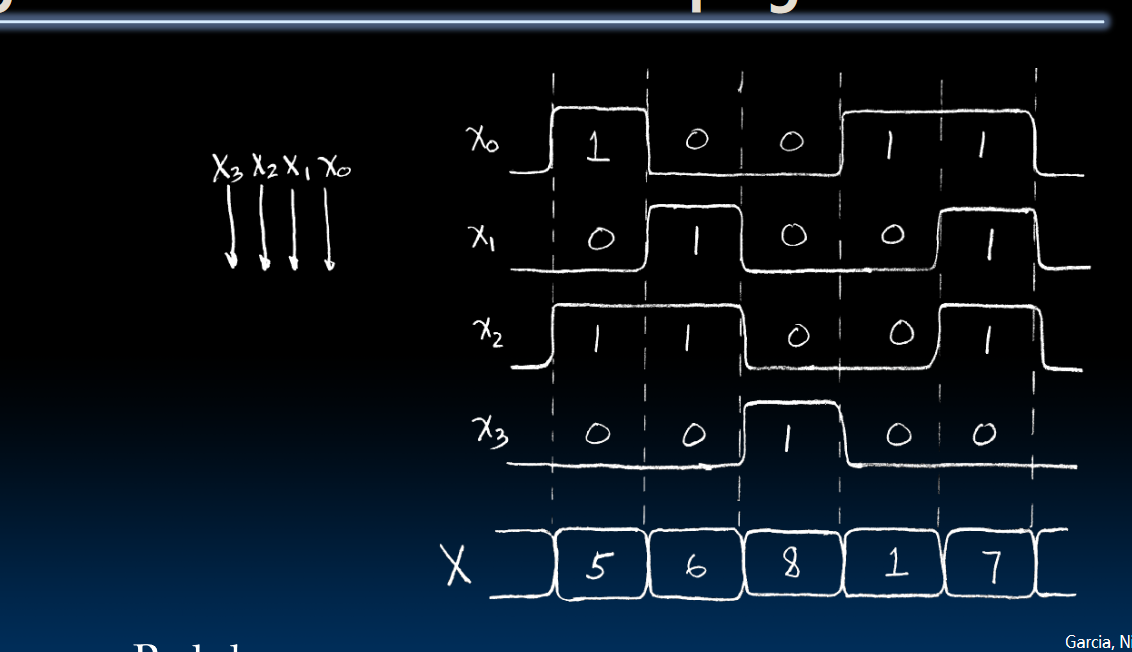

集群(Grouping)

将头往左偏,X的结果从左到右分别是1010、0110、0001、1000、1110

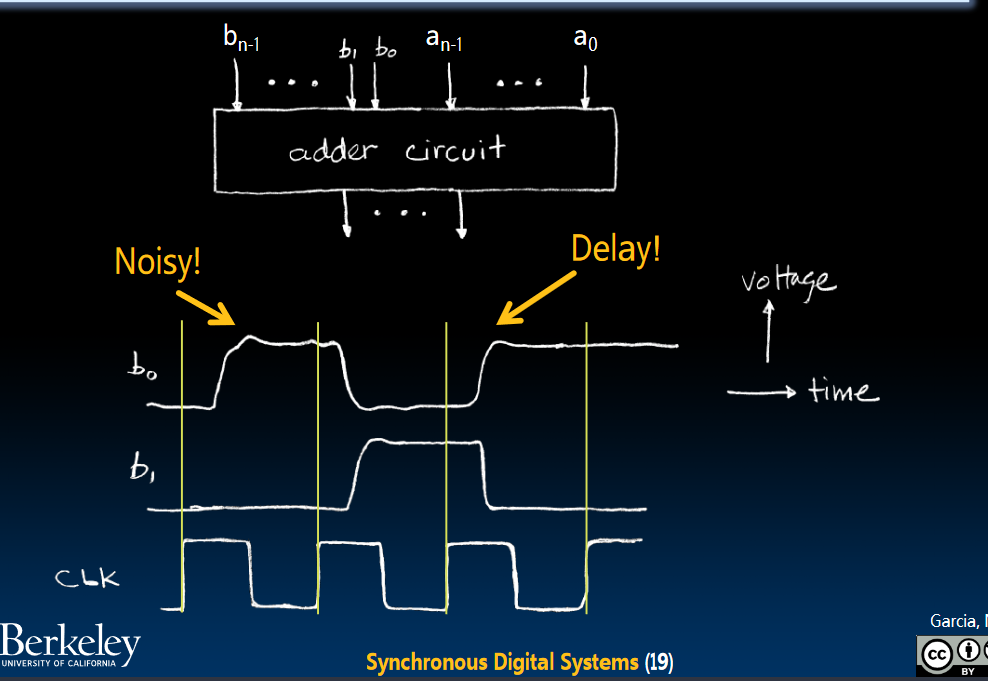

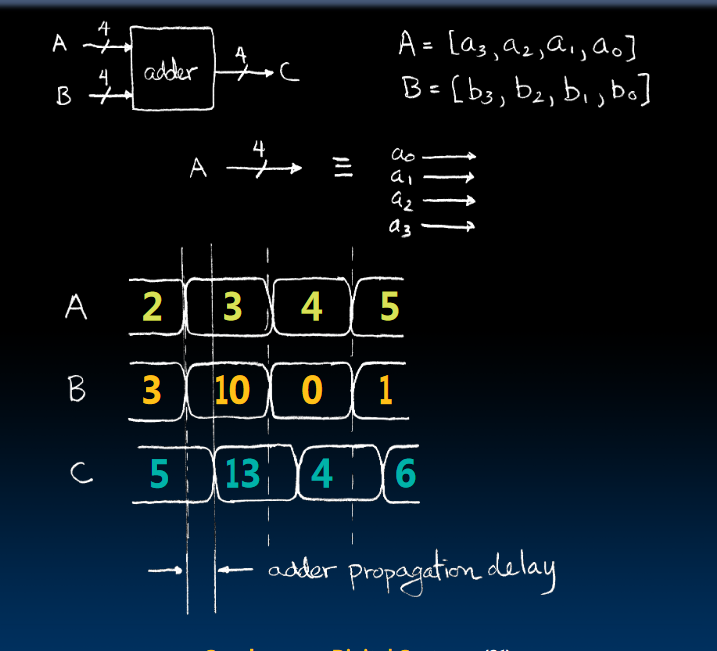

电路延迟

电路类型

- 同步数字系统由两种基本类型的电路组成:

- 组合逻辑( CL )电路

- 我们前面的加法器电路就是一个例子,

- 输出仅是输入的函数,

- 类似于数学中的纯函数,y = f ( x )。(没有办法存储从一次调用到下一次的信息。无副作用)

- 组合逻辑可能有延迟,但是没有反馈,没有状态。输出只是 输入的函数。

- 状态元件

- 存储信息的电路

状态元素来 存储我们的数据、寄存器、缓存、内存、磁盘。所有这些东西都有状态。他们记得 你放在那里的东西。

有状态的电路

https://youtu.be/EQYtPrBWvrU?list=PLnvUoC1Ghb7wJLSxkK0XWdHYjav1Tl3Z9&t=548

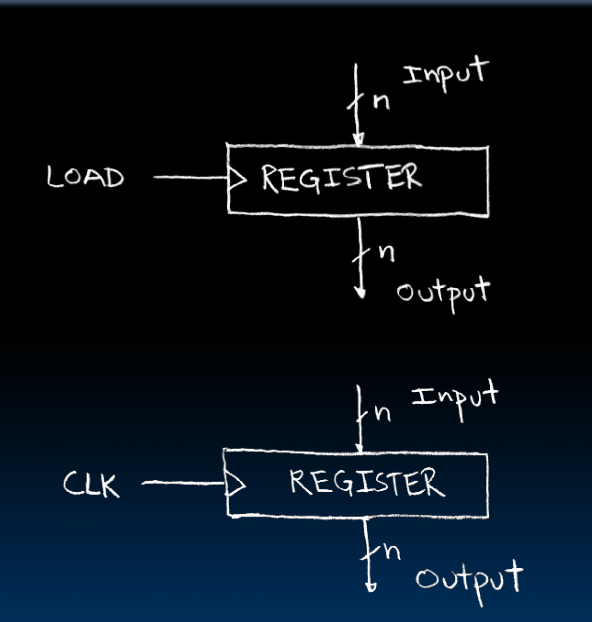

这称为寄存器(

- 它有 n 位输入,n 位 输出,并且有一个加载器。这个小电路表明, 当该电路变高时,会发生一些神奇的事情。因此,当该值变高时, 寄存器将执行以下操作:

- 假如我是一个登记员,我朝向Output一端

- 当负载升高时,我转身,获取输入的值并保留它然后转向output输出

- 当负载变小,无论我背后(input)有什么值,我都不在乎

小总结

时钟控制我们电路的脉冲

§电压为模拟量,量化为0 / 1

§电路延迟是生活的事实

两类电路:

- 无状态组合逻辑( & , | , ~)

- 有状态电路(例如,寄存器)

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 云泥小窝!

评论